# USB4<sup>™</sup> Cable Electricals and System Design

**Yun Ling** – USB Newark Mechanical WG Co-Chair **Reza Zamani** – Signal Integrity Engineer, Intel

USB Developer Days 2019 – Taipei, Taiwan November 20, 2019

USB Type-C<sup>®</sup>, USB-C<sup>®</sup> and USB4<sup>™</sup> are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). Thunderbolt<sup>™</sup> is a trademark of Intel Corporation. All product names are trademarks, registered trademarks, or service marks of their respective owners.

USB Implementers Forum © 2019

#### Agenda

- Cable Electricals

- Electrical Spec

- Cables

- Mated Connectors

- Design Challenges

- Compliance Test

- System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometries

- Routing practices, vias, and component placements

- Layout design

- Component selection

# Cable Electricals

Yun Ling, Sr. Principal Engineer, Intel

USB Implementers Forum © 2019

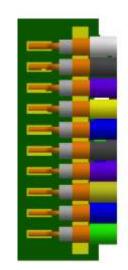

#### **USB Type-C<sup>®</sup> Cables and Connectors**

Looking into the product receptacle:

| A1  | A2   | A3   | A4   | A5   | A6 | A7 | A8   | A9   | A10  | A11  | A12 |

|-----|------|------|------|------|----|----|------|------|------|------|-----|

| GND | TX1+ | TX1- | Vbus | CC1  | D+ | D- | SBU1 | Vbus | RX2- | RX2+ | GND |

|     |      |      |      |      |    |    |      |      |      |      |     |

| GND | RX1+ | RX1- | Vbus | SBU2 | D- | D+ | CC2  | Vbus | TX2- | TX2+ | GND |

| B12 | B11  | B10  | B9   | B8   | B7 | B6 | B5   | B4   | B3   | B2   | B1  |

- Focus on C-to-C cable high speed elect

- No change to mechanical spec

#### **USB4™ Gen2 Cable Spec**

- USB4 Gen2 cable electrical spec is identical to USB3.2!

- It uses the same integrated Sparameters, avoiding the Sparameter mask as much as possible.

- Key spec items include:

- Insertion Loss Fit at Nyquist

- Integrated Multi-Reflection

- Integrated Return Loss

- Integrated Crosstalk

S-parameter mask-based spec creates too many false failure cases!

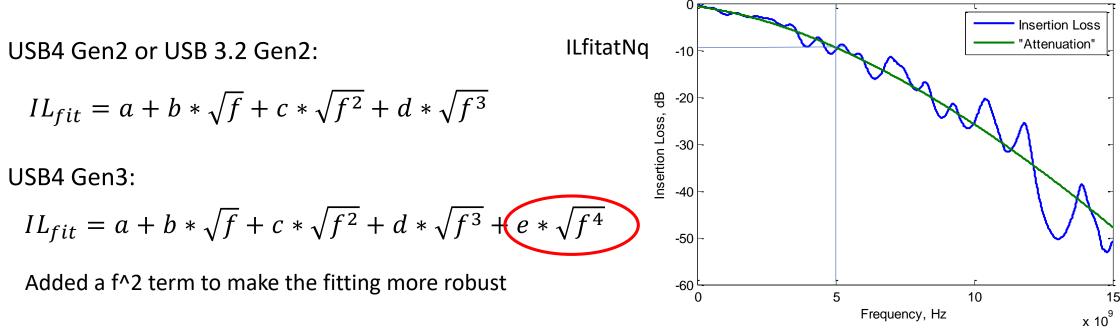

#### **Insertion Loss Fit and Multi-Reflection**

- Insertion loss, IL(f), represents the remaining signal after it travels thru the cable.

- IL(f) may be decomposed into Insertion loss fit, IL\_fit(f) and multi-reflection, MR(f).

- IL\_fit: uses a smooth function to fit the IL, representing the signal.

- MR = IL IL\_fit, representing the multi-reflection noise.

- IL fit at Nyquist frequency = IL\_fit (Nyquist frequency):

#### System loss budget

- Host/device loss includes everything in the signal path from die to connector tongue.

- USB4 Gen2 supports a 12 dB (2m) cable while USB3.2 Gen2 support only a 6 dB (1m) cable due to the difference in system loss budget.

- Host/device loss budgets are informative only.

|                       | Host   | Cable  | Device | Total |

|-----------------------|--------|--------|--------|-------|

| USB3.2 Gen2 (10 Gbps) | 8.5 dB | 6 dB   | 8.5 dB | 23 dB |

| USB4 Gen2 (10 Gbps)   | 5.5 dB | 12 dB  | 5.5 dB | 23 dB |

| USB4 Gen3 (20 Gbps)   | 7.5 dB | 7.5 dB | 7.5 dB | 23 dB |

# **Insertion Loss Fit Spec**

- USB 3.2 Gen2

- $\geq$  -4 dB at 2.5 GHz

- $\geq -6 \text{ dB}$  at 5 GHz

- $\geq$  -11 dB at 10 GHz

- USB4 Gen2 (2m)

- $\geq$  -7.0 dB at 2.5 GHz

- > −12 dB at 5 GHz

- USB4 Gen3

- $\geq -1 \text{ dB}$  at 100 MHz

- $\geq$  -4.2 dB at 2.5 GHz

- $\geq$  -6 dB at 5 GHz

- $\geq -7.5 \text{ dB} \text{ at } 10 \text{ GHz}$

- ≥ -9.3 dB at 12.5 GHz

- $\geq -11 \text{ dB}$  at 15 GHz

- Cable length mentioned in the spec is for reference only. Performance spec dictates cable length.

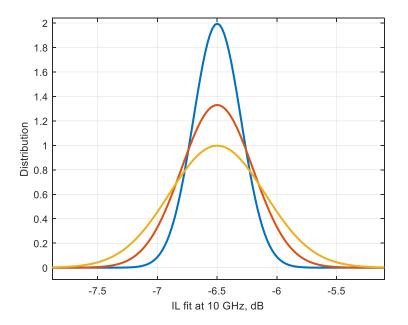

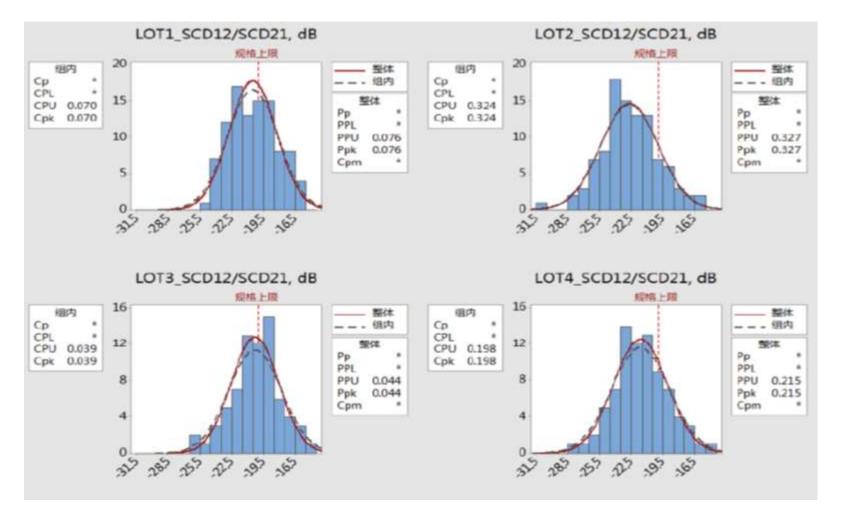

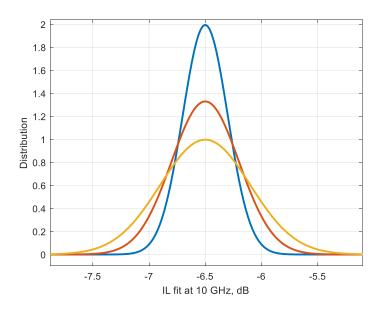

- Consideration to HVM variation is a must!

- Spec is meant for the worst-case, not the mean value. For example, to meet the ≥ -7.5 dB

IL\_fit\_at\_10GHz spec, the mean has to be significantly > -7.5 dB to account for HVM variation

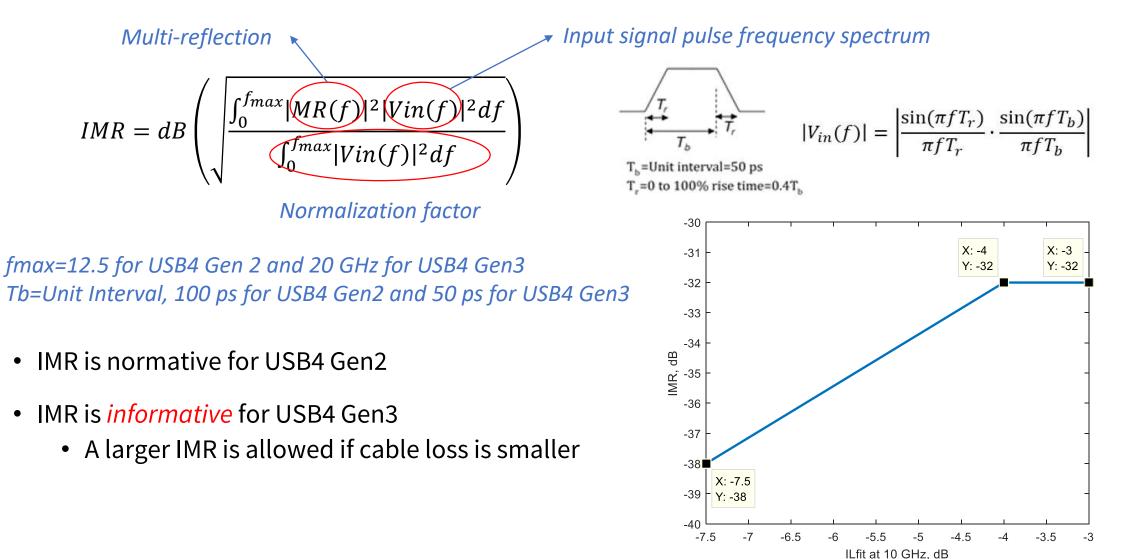

#### **Integrated Multi-Reflection Spec**

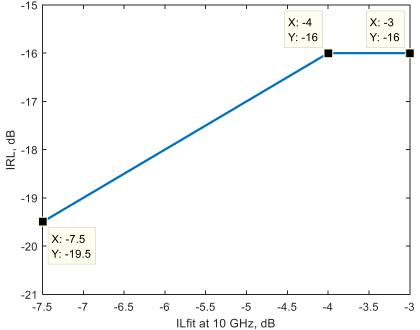

#### **Integrated Return Loss**

$$IRL = dB\left(\sqrt{\frac{\int_{0}^{f_{max}} |Vin(f)|^{2} |SDD21(f)|^{2} (|SDD11(f)|^{2} + |SDD22(f)|^{2}) df}{\int_{0}^{f_{max}} |Vin(f)|^{2} df}}\right)$$

Integrated Return Loss measures the undesired interaction/reflection between the cable and host/device.

- IRL is a normative requirement.

- More IRL is allowed if cable loss is smaller

USB Implementers Forum © 2019

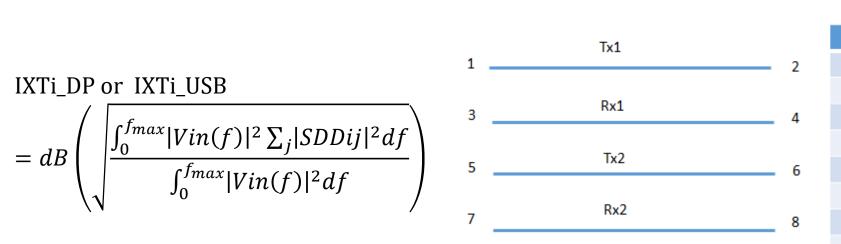

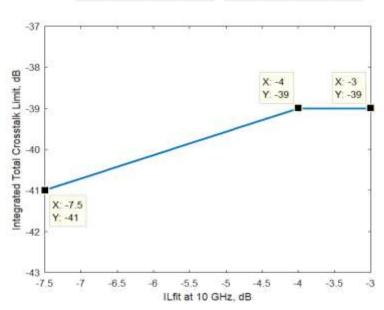

#### **Integrated Crosstalk**

#### i=victim; j=aggressor

IXT\_USB

2

-3

IXT DP

6

3

- USB4 Gen3 specifies the combined total crosstalk in USB mode and DP alt-mode.

- USB mode: 2 NEXT +1 FEXT

- DP mode: 3 FEXT

- It is a better way to control crosstalk as compared to specify crosstalk between each pairs.

- Easier to meet the spec for the same effect

USB Implementers Forum © 2019

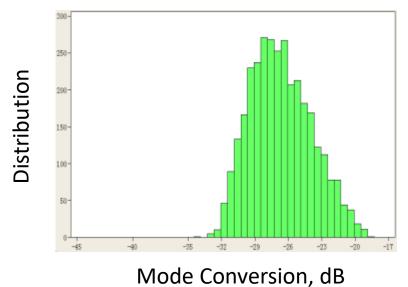

#### **Mode Conversion**

• Mode conversion is relaxed from -20 dB to -17 dB (to 10 GHz) for USB4 Gen3 due to industry capability reality

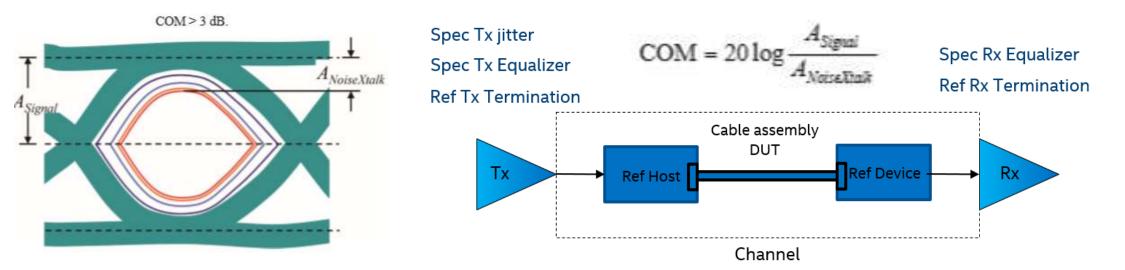

# **COM – Channel Operation Margin**

- COM is a figure of merit to measure channel electrical quality defined by IEEE 802.3. It is a Signal-to-Noise Ratio developed in a similar way to Statistical Analysis

- Collaterals needed to calculate COM:

- Measured cable S-parameters

- Reference hosts/devices

- Reference Tx/Rx termination

- COM configuration file

## **Reference Host – 1/2**

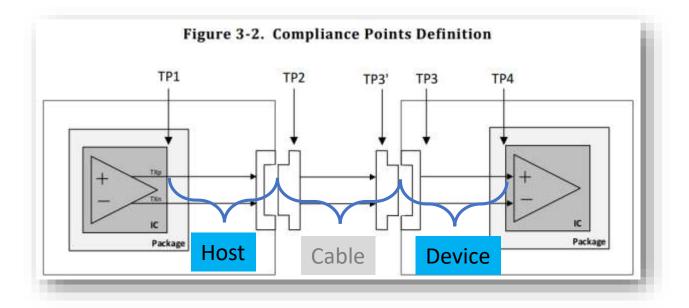

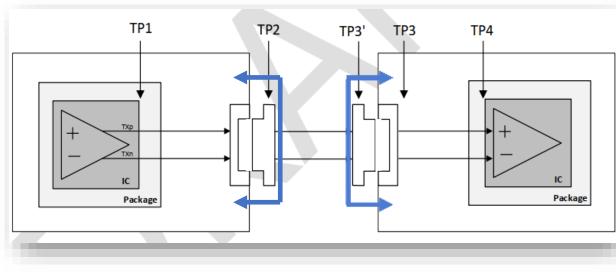

• Topology of the Reference Host/device

Die model is used for collection of Insertion Loss and Return Loss. <u>But</u> <u>it is not in the reference host</u>

Drv

#### Components of Reference Host Model √ia#' MS TL MS TL MS TL MS T MS TL (0201 220K USB-C AC-(Only (Only Tx2, PKG Тор ESD Тор Тор (Bottom +idea Cap Tx2 Receptacle Layer Lavei Layer Rx1) Layer) 12.2) Rx1 Return Loss is

- Variables permutations from which two reference hosts are selected

- Impedance of traces

- Attenuation of traces

- Trace length

- Location of the ESD

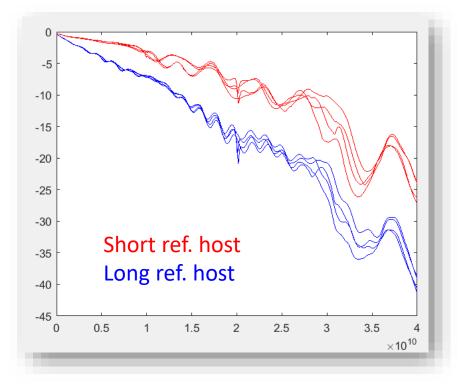

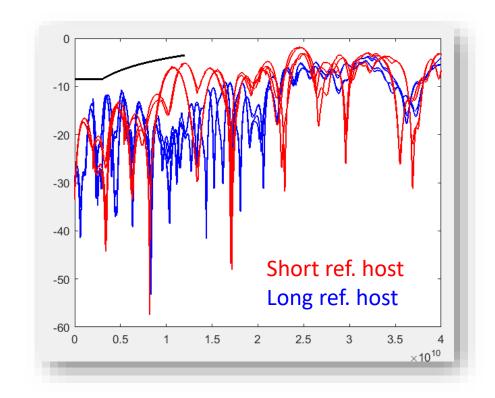

Two reference hosts/devices are defined: long host/device and short host/device. Long host/device has about -7.5 dB loss at 10 GHz (with die-loading) Short host/device has the minimum loss possible

USB-C

Mated

measured

here

#### **Reference Host – 2/2**

• Insertion loss up to receptacle's tongue include die load

Return loss at TP2 (w/ die load attached)

# COM Config File for USB4<sup>™</sup> Gen3

- All equalization settings are based on the USB4 Specification.

- Tx FFE

- RX CTLE and DFE

- Tx random jitter and deterministic jitter are derived from the USB4 specification.

- The input voltage swing (A\_v, A\_fe, and A\_ne) is assumed to be the typical range of 0.8 to 1.2 V (differential peak-to-peak)

| Parameter        | Setting                               | Unit    | Information                                                                                           |

|------------------|---------------------------------------|---------|-------------------------------------------------------------------------------------------------------|

| f_b              | 20                                    | GBd     | USB4 Gen 3 data rate                                                                                  |

| C_d              | [0 0]                                 | nF      | Tx and Rx capacitive loading. It is set to zeros as the die-loading is treated as part of the channel |

| R_d              | [42.5 42.5]                           | Ohm     | Tx and Rx termination resistance                                                                      |

| ffe_preset       | Table 3-4 of<br>USB4<br>Specification |         | Tx equalization presets                                                                               |

| g_DC             | [-9:1:0]                              | dB      | CTLE DC gain                                                                                          |

| f_p1             | 5                                     | GHz     | CTLE pole 1                                                                                           |

| f_p2             | 10                                    | GHz     | CTLE pole 2                                                                                           |

| f_z              | 3.55                                  | GHz     | CTLE zero                                                                                             |

| A_v              | 0.4                                   | V       | Signal swing                                                                                          |

| A_fe             | 0.4                                   | V       | FEXT aggressor swing                                                                                  |

| A_ne             | 0.6                                   | V       | NEXT aggressor swing                                                                                  |

| N_b              | 1                                     |         | Number of DFE tap                                                                                     |

| b_max(1)         | 0.7                                   |         | DFE bound, ratio to cursor                                                                            |

| Sigma_RJ         | 0.01                                  | UI      | Tx ramdom jitter, rms.                                                                                |

| A_DD             | 0.085                                 | UI      | Tx deterministic jitter, mean-to-peak                                                                 |

| DER_0            | 1e-12                                 |         | Target raw bit-error-rate                                                                             |

| eta_0            | 3.3e-8                                | V^2/GHz | One sided noise spectral density                                                                      |

| SNR_TX           | 40                                    | dB      | Tx signal to noise ratio                                                                              |

| COM<br>Threshold | 3                                     | dB      | Pass/fail criterion                                                                                   |

#### **Spec Validation**

- Spec cables: "worst-case" cables that hit the spec limits at various ILfit @10 GHz.

- The spec cables marginally pass/fail COM

- Measured cables: measured TBT3 cables from different vendors

- Almost all known TBT3 cables pass the integrated parameter and COM spec.

| Host# | Device# | Cable#           | Victim | ILfitatNq | Signal_m\ | ISI_mV | Crosstalk_ | сом      | COM Limi | Pass/Fail | Integrated Parameter |

|-------|---------|------------------|--------|-----------|-----------|--------|------------|----------|----------|-----------|----------------------|

| 1     | L 1     | Spec long cable  | Tx2    | -22.9182  | 47.53322  | 20.7   | 7.86       | 2.925708 | 3        | Fail      | Border Line          |

| 2     | 2 2     | Spec short cable | Tx2    | -11.0043  | 142.7662  | 72.44  | 17.72      | 2.936699 | 3        | Fail      | Border Line          |

| 1     | ι 1     | Measured Cable25 | Tx2    | -21.2287  | 53.99262  | 21.53  | 6.62       | 3.862656 | 3        | Pass      | Pass                 |

| 1     | L 2     | Measured Cable26 | Rx1    | -17.7044  | 76.09064  | 28.88  | 21.9       | 2.681497 | 3        | Fail      | Fail IXT             |

| 1     | L 1     | Measured Cable27 | Tx2    | -22.2626  | 50.48604  | 21.25  | 6.17       | 3.528888 | 3        | Pass      | Pass                 |

| 1     | ι 1     | Measured Cable29 | Rx1    | -22.7136  | 49.78228  | 21.08  | 5.83       | 3.45617  | 3        | Pass      | Pass                 |

| 1     | L 1     | Measured Cable30 | Tx2    | -21.4544  | 54.79757  | 22.36  | 7.8        | 3.683021 | 3        | Pass      | Pass                 |

| 1     | L 1     | Measured Cable31 | Rx1    | -21.2108  | 53.77911  | 23.54  | 6.63       | 3.375939 | 3        | Pass      | Pass                 |

| 1     | L 1     | Measured Cable33 | Tx2    | -22.299   | 49.82818  | 22.82  | 5.46       | 3.150423 | 3        | Pass      | Pass                 |

| 1     | ι 1     | Measured Cable32 | Tx2    | -19.5524  | 66.52476  | 33.3   | 12.65      | 2.522059 | 3        | Fail      | Fail IRL             |

| 1     | L 1     | Measured Cable22 | Tx1    | -19.9512  | 64.03106  | 28.25  | 10.45      | 3.248895 | 3        | Pass      | Marginal on IRL      |

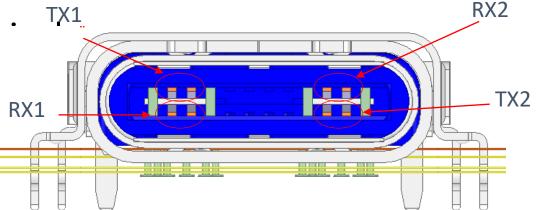

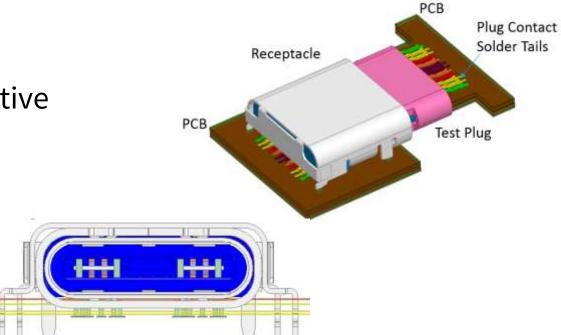

#### **Mated Connector Spec**

- USB 3.2 and USB4 Gen 2 have only the informative receptacle/mated connector electrical spec.

- But for USB4 Gen3, the this is Normative.

- Need to define the "Golden Plug".

| Parameter | Requirements                                                                                                                                                  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IL fit    | <ul> <li>≥ -0.6 dB @ 2.5 GHz</li> <li>≥ -0.8 dB at 5.0 GHz</li> <li>≥ -1.0 dB @ 10 GHz</li> <li>≥ -1.25 dB @ 12.5 GHz</li> <li>≥ -1.5 dB @ 15 GHz5</li> </ul> |

| IMR       | ≤ –39 dB                                                                                                                                                      |

| INEXT     | ≤ -43 dB                                                                                                                                                      |

| IFEXT     | ≤ -43 dB                                                                                                                                                      |

| Parameter                                       | Requirements                    |

|-------------------------------------------------|---------------------------------|

| IDDXT (Corsstalk<br>between Tx/Rx and<br>D+/D-) | ≤ -50 dB                        |

| IRL                                             | ≤ −15 dB                        |

| SCD12/SCD21 (Mode<br>Conversion)                | ≤ -20 dB (100 MHz to<br>10 GHz) |

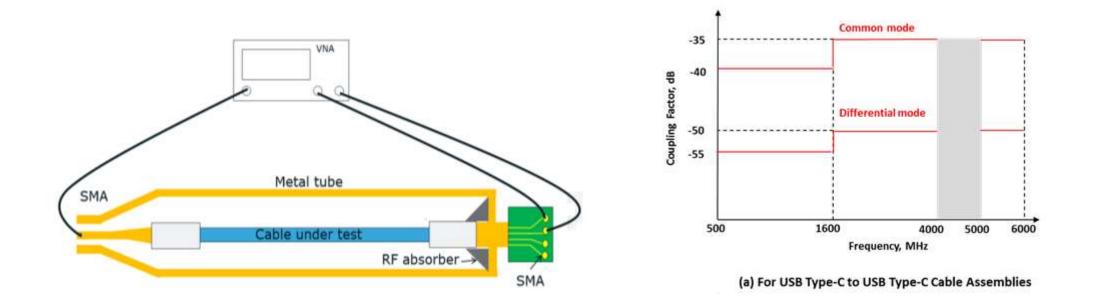

#### **Cable Shielding Effectiveness**

• The same shielding effectiveness requirement for USB 3.2 Type-C-to-Type-C cables is applicable for the USB4 cables.

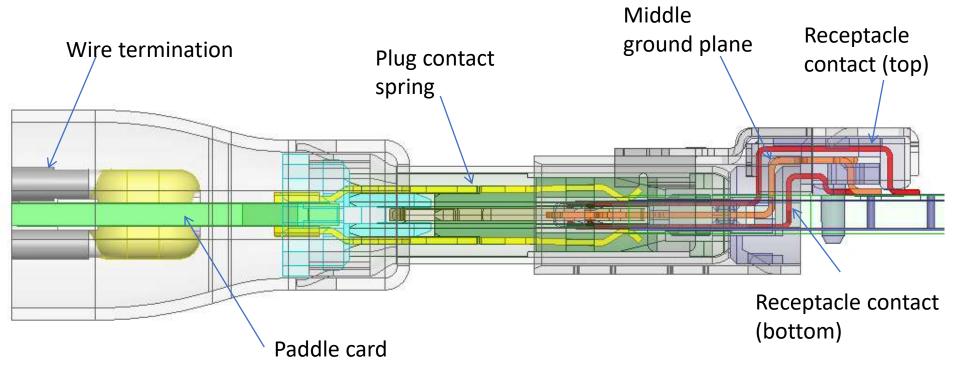

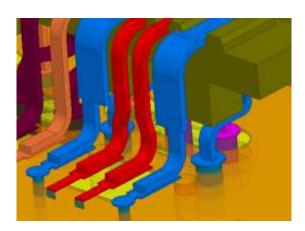

## **Design Challenges**

- USB4 Gen3 has tighter electrical requirements for cables and connectors.

- Everything along the signal path should be optimized.

- Loss, reflection, crosstalk

# **Design for Signal Integrity**

- Raw cable managing loss and skew

- Loss per inch

- Skew

- Impedance

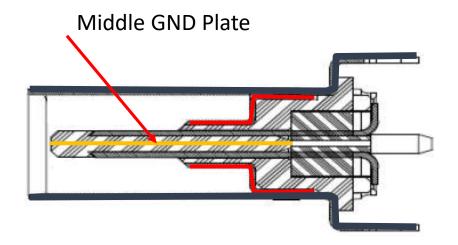

- Connector minimizing discontinuities

- Footprints

- Contact geometries

- Middle GND plates

- Paddle card isolating coupling

- Pin/wire-out

- Footprints

- Layer count

- Wire termination

#### **Compliance Test**

- The USB4 Gen3 cable compliance spec is still under development.

- The goal is to have a robust cable/connector eco-system without prohibitive cost adders.

- Key challenges:

- How to ensure the worst-case cable (within HVM limits) passes the spec?

- How to check if a certified cable will continue to meet the spec?

#### **USB4™ cable Spec Summary**

- The main spec items for USB4 Gen3 cables are:

- Insertion fit (normative)

- IMR (informative)

- IRL (normative)

- IXT\_USB/IXT\_DP (normative)

- COM (normative)

- Mode conversion

- Shielding effectiveness

- USB-IF will provide necessary supporting collaterals to extract/calculate the spec parameters

- Tools and models

- The USB4 Cable/Connector Compliance Spec is still under development.

# USB4<sup>™</sup> System Design Guidelines

Reza Zamani– Intel

USB Implementers Forum © 2019

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

#### **Host and Device Interconnects**

- This presentation covers three categories of design considerations for the host and device interconnects/channels:

- 1. Electrical

- 2. Physical/Layout

- 3. Component selection and specifications

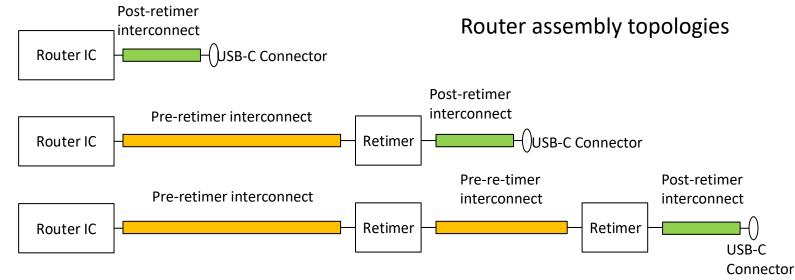

# **Pre-Retimer and Post-Retimer Interconnects**

- Various topologies of the router assembly is shown

- For this presentation, let's say we have two categories of interconnects. These have differences and demand potentially different design priorities. This presentation covers both

| Pre-Retimer Interconnect                                                                                                                                                                                                                                                                     | Post-Retimer Interconnect                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>No explicit electrical/compliance target. Dependent on Tx and Rx PHYs at either ends.</li> <li>Likely long =&gt; insertion loss becomes a design priority =&gt; PCB stack up selection, trace geometry optimization, etc.</li> <li>Has fewer discrete components: AC-cap</li> </ul> | <ul> <li>Explicit electrical/compliance design targets defined per the spec</li> <li>Likely short =&gt; return loss becomes a design priority</li> <li>Has more discrete components: AC-cap, ESD, bleed resistor, etc. =&gt; component selection, placement and routing are important</li> </ul> |

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

# **Electrical Design Considerations**

- Insertion Loss: The informative differential Insertion loss of the router assembly from the receptacle's tongue to the USB4 transceiver is limited to:

- This includes the die load, IC package, PCB routing, discrete components, and receptacle's tongue

- Note that the USB4 Gen2's host budget is smaller than USB3.2's. This is for supporting a 2m cable

| f<br>B4 | Router Assembly<br>Support | <i>Informative</i><br>Insertion Loss Limit |  |  |  |

|---------|----------------------------|--------------------------------------------|--|--|--|

| ▶       | USB4 <b>Gen 3</b>          | < <b>7.5 dB</b> at 10GHz                   |  |  |  |

|         | USB4 <b>Gen 2</b>          | < <b>5.5 dB</b> at 5GHz                    |  |  |  |

|         |                            |                                            |  |  |  |

|         | USB3.2                     | < 8.5 dB at 5GHz                           |  |  |  |

- **Tx and Rx Compliance Tests:** The router assembly must meet Tx and Rx compliance. Even though performance of the silicon affects most of the compliance metrics, performance of the interconnect will impact the following

- Tx and Rx return loss

- Total Jitter (TJ) is impacted by the way of:

- 1. Tx data dependent jitter (DDJ), which is impacted primarily by the insertion loss

- 2. Cross talk in the interconnect contributes to Uncorrelated Deterministic Jitter (UDJ)

- Rx stressed eye test (a.k.a. BER tolerance test)

- Secondary effect on a few other compliance metrics, e.g. Tx AC Common mode voltage, etc.

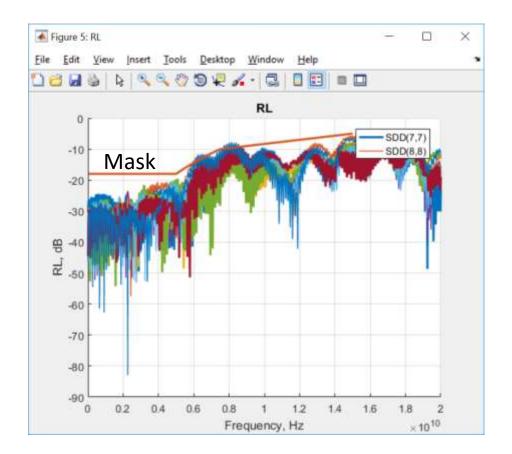

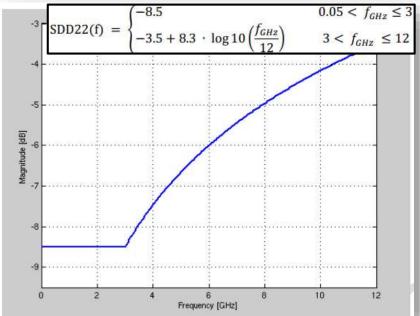

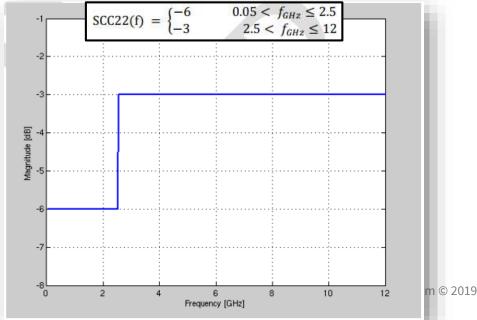

#### **Return Loss Spec**

- The Return loss spec defined at TP2 for Tx and TP3' for Rx

- The necessary VNA measurements are collected with a compliance plug test board (See 3.3.6.1)

- The measurement shall be referenced to single-ended impedance of 42.5  $\boldsymbol{\Omega}$

- The differential return loss for both Tx and Rx shall not exceed

The common mode return loss for both Tx and Rx shall not exceed

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

#### **Trace Geometry and Impedance**

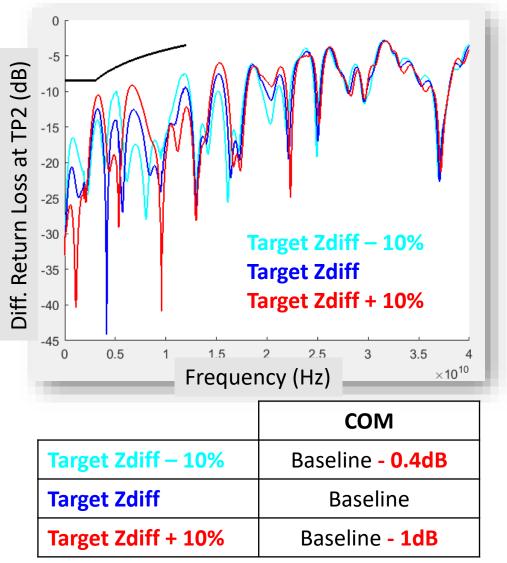

- Choose a trace geometry (width and spacing) that yields nominal differential impedance of 80-85

Ohms

- For short interconnects, the exact value in that range may be of importance. Recommend COM or return loss simulations to find the optimized value

- For long channels, the exact impedance in the range is not that important. Trace loss/attenuation should become the primary design concern

- Consider the variation of impedance when assessing your design. This is important for short interconnects

- Example: notice the impact of impedance variation on return loss and on COM

#### **Trace Geometry and Loss/Attenuation**

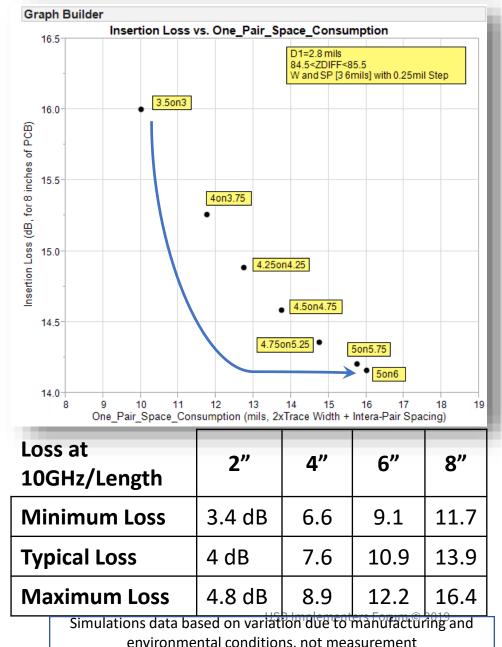

- If your objective is long reach, reduce the attenuation of traces by optimizing the trace geometry

- The PCB vendor's recommended minimum trace width/spacing likely have not optimized loss

- **Design Tip:** you can spend more area (i.e. larger trace width and/or spacing) to reduce loss.

- Example: for 8" of microstrip trace, the differential loss can be cut from 16dB @ 10GHz to ~14dB by optimizing the trace width/spacing from 3.5/3 mils to 5/6 mils

- Consider the variation of loss when assessing your design. See the table for an example

- Note that aside from manufacturing variations, temperature and humidity can impact attenuation of traces

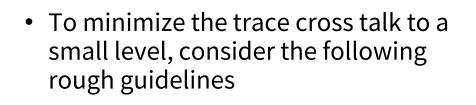

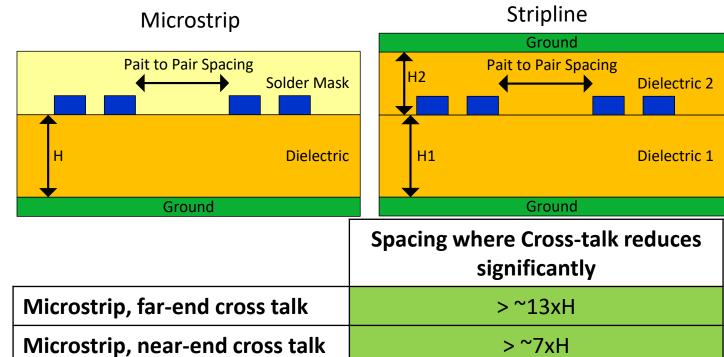

## **Trace Geometry and Cross Talk**

2

6

- Pair-to-pair spacing (P2PS) modulates the cross talk contribution from the traces.

- Let us define pair-to-pair spacing as a multiple of dielectric height. Example, P2PS=20xH (for stripline, H = min(H1, H2))

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

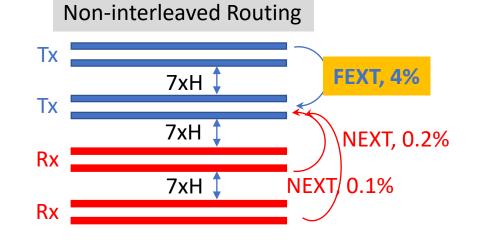

# **Routing on Microstrip Layer**

- Routing on microstrip presents a challenge from far-end cross talk (FEXT) between two adjacent Tx or Rx pairs which increases as routing length increases

- Example: an 8" of routing can have up to 4% FEXT when spacing is 7xH

- Mitigation options:

- Use more than one layer to avoid placing two Tx or Rx pairs adjacent to each other

- Use large spacing as shown in previous slide

| Microstrip, far-end cross talk | Spacing > ~13xH |

|--------------------------------|-----------------|

| • *                            |                 |

Consider interleaved routing, where you can increase the effective distance between two Tx or Rx without spending more board area. The trade-off is some additional near-end cross talk (NEXT)

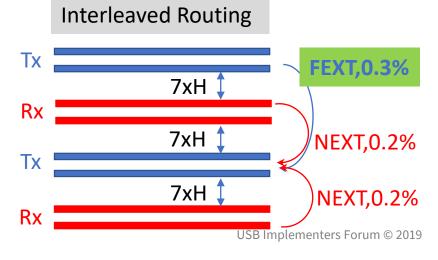

### **Vertical Transitions**

• Avoid via stubs or minimize the length of the stub. Long stubs will negatively impact return loss, insertion loss, (hence ISI, hence DDJ), and ultimately end to end margins (e.g. COM)

- As mitigation options, consider the following

- 1. Optimize impedance discontinuity by adjusting via pitch, diameter, pad/anti-pad size

- 2. Other via technologies: Back-drilled via or uVia (Type-4 PCB)

- 3. Routing only on surface layers

- 4. If a via stub is inevitable, assess your design w/ return loss or COM simulations.

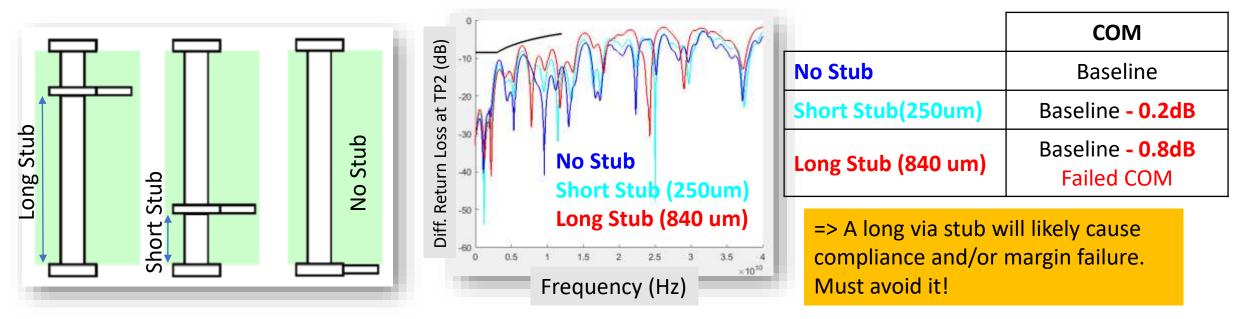

#### **Component Placement**

- Each device/components presents an impedance discontinuity because of its internal structure as well as its parasitic (e.g. its SMT pads)

- Placing as many discontinuities (devices, SMT components, vias, etc) as you can close to each other can help improve return loss (hence ISI, hence DDJ) and/or end to end margins (e.g. COM)

- **Design Tip:** Avoid placing the ESD, ac-cap, and bleed resistors halfway between the IC package and the USB-C connector. Try to place them closer to either the IC package or the USB-C connector.

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

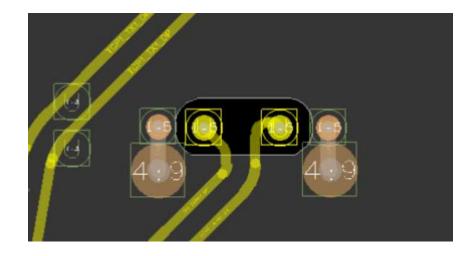

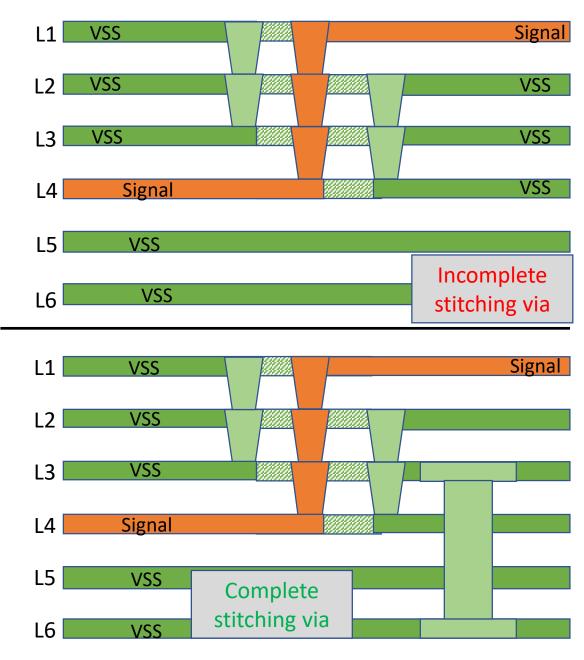

#### Layout Design Guidelines -1/7

- With signal vias, there needs to be proper stitching/return vias. For instance, a L1-L4 transition requires stitching via from L2 to L3 as well as L5 (L3 and L5 are reference planes for trace when it is routed on L4). **Pay special attention to this on Type4 PCBs**

- Symmetric placement of stitching vias is desired to minimize mode conversion

### Layout Design Considerations/Examples - 2/7

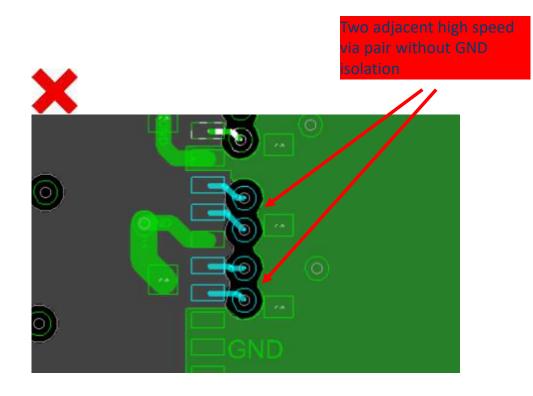

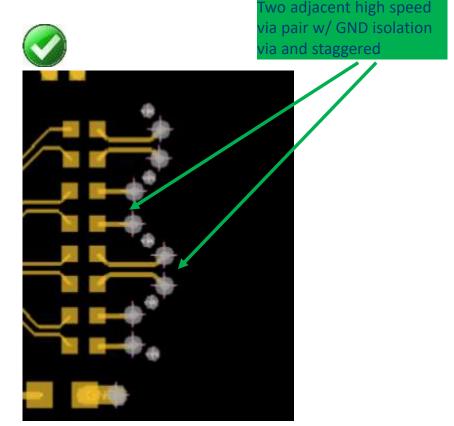

- Adjacent via pairs must be isolated with GND vias to minimize cross talk

- Staggering the via pair left and right should provide room for placing GND via

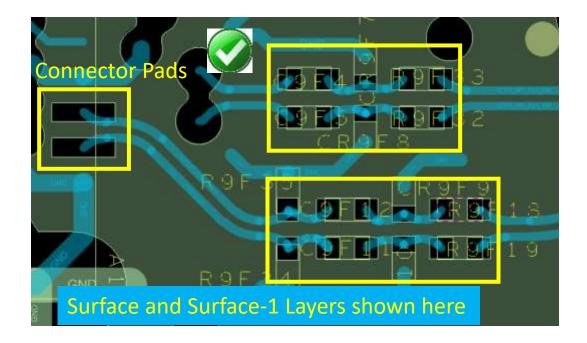

#### Layout Design Considerations/Examples - 3/7

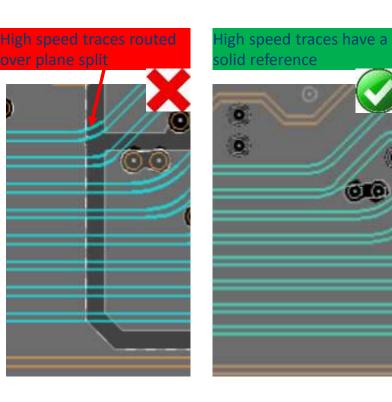

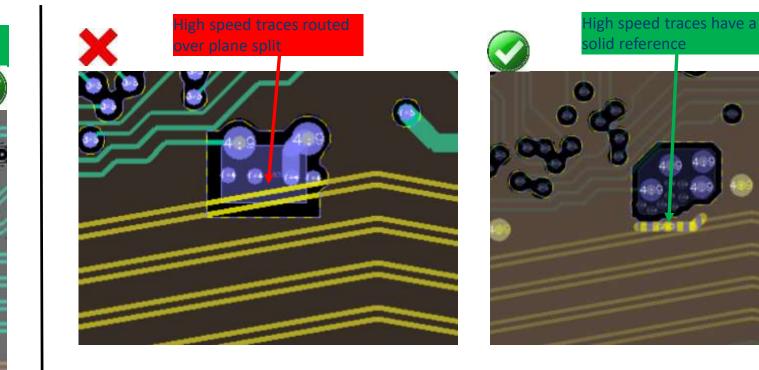

• USB4 traces should not be routed over voids or reference plane splits

OIO

• In face, it's best to maintain a 3xH (H: height of dielectric) between trace edge and void to minimize impedance discontinuity and mode conversion

### Layout Design Considerations/Examples - 4/7

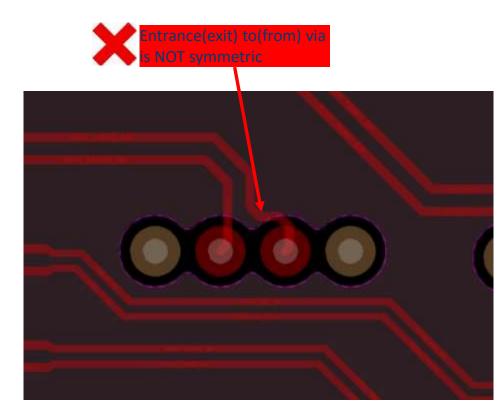

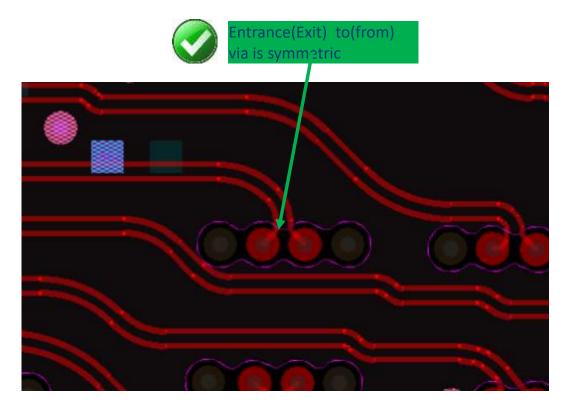

• Entrance to and exit from vias should be symmetric

## Layout Design Considerations/Examples - 5/7

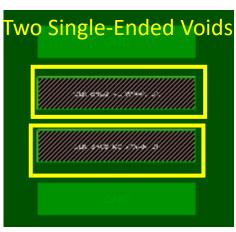

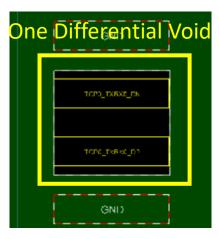

• Void under SMT pads for better SI. The larger the pad size, the more important this is

• Ensure that layer under the void (surface-2) is not a source of noise, e.g. power plane. It's best to have ground on surface-2 under the void

- Single-ended voids are recommended for most cases/components

- Differential voids for larger pads and/or thin dielectric height (<~60um)</li>

- These voids can overcompensate (increase impedance too much).

So analysis/3D modeling may be needed

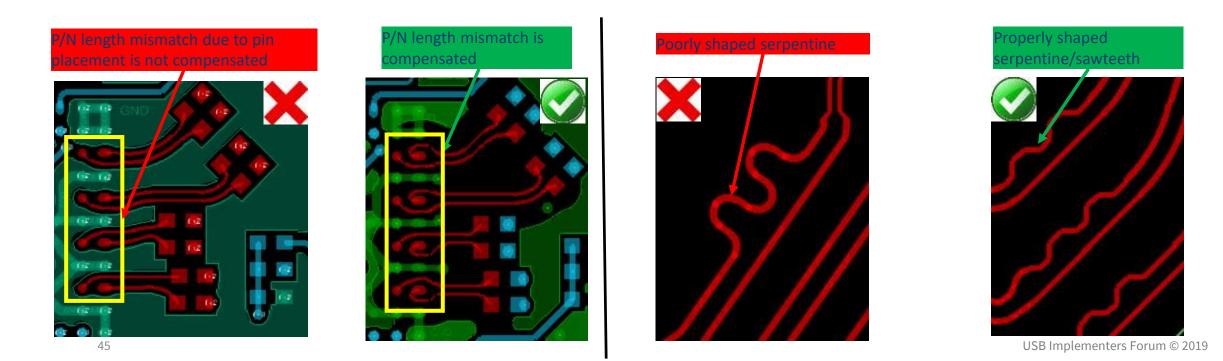

## Layout Design Considerations/Examples - 6/7

- P/N length mismatch may be inevitable (due to pin out for example). Adequate P/N length matching should be considered. Any technique to achieve matching should consider the following:

- P/N length matching should occur as close as possible to where the mismatch happens

- Serpentine/sawtooth routing is a way to reduce P/N length mismatch, but shape of serpentine/sawtooth should be optimized

### Layout Design Considerations/Examples - 7/7

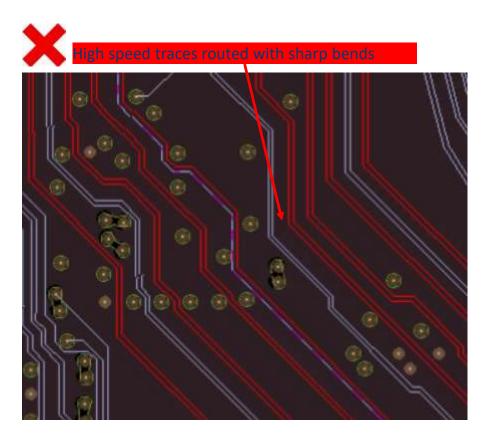

• The bends on USB4 traces should be smoothened. This should improve return loss at high frequencies

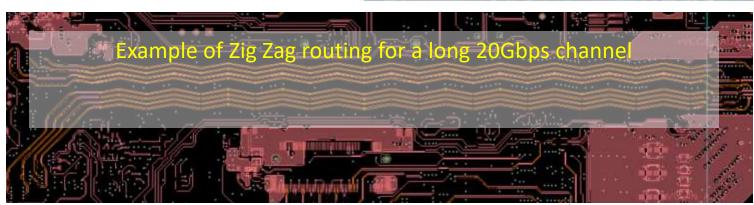

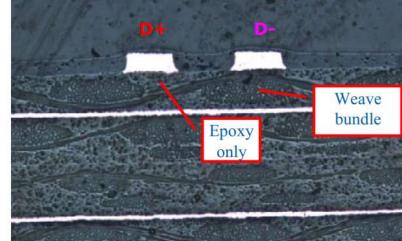

## **Fiberweave Effect**

- PCBs are constructed from woven fiberglass fabric bound together with epoxy resin. The glass and epoxy have different dielectric constants.

- One half of a differential pair can run over epoxy and the other half over glass weave. Therefore, propagation delay is different between D+ and D- causing skew, which causes degraded insertion loss as well as common mode noise (i.e. mode conversion)

- The degradation increases as the length of trace increases

- Mitigation options are required for USB 4speeds

- Layout mitigation techniques:

- Angled routing

- Zig-zag routing

- PCB vendor rotates image of the board

- Tighter weaves

- Many more ....

#### USB4™ System Design Guidelines

- Electrical Design Considerations

- Physical Design Considerations

- Trace geometry

- Routing practices, vias, and component placement

- Layout design

- Component selection

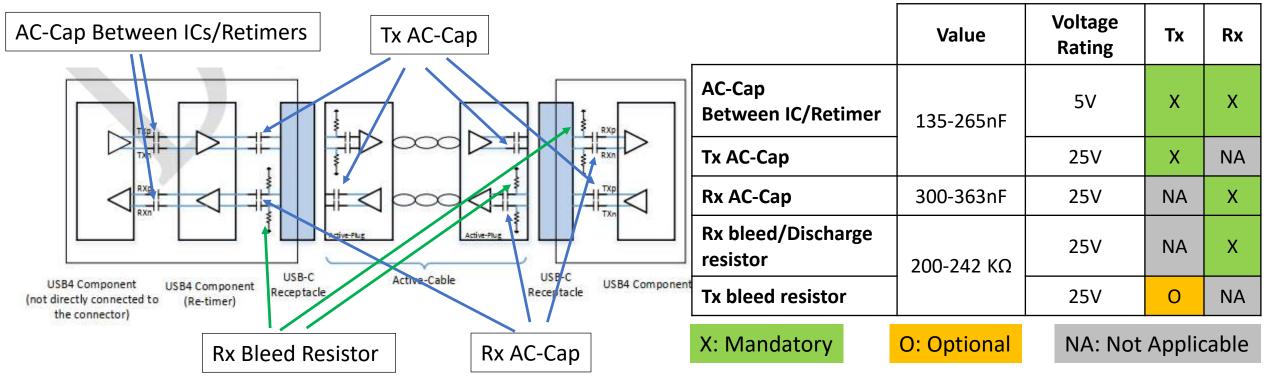

## **AC-Caps and Discharge Resistors**

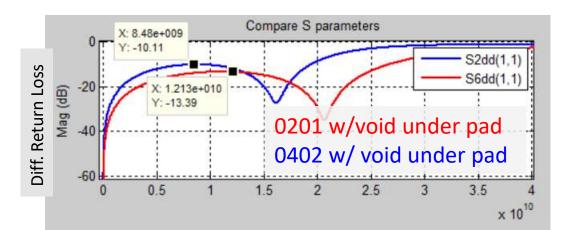

• Smaller size components (e.g. 0201) will have smaller parasitic and therefore better return loss than larger ones (0402). Consider using 0201 components

#### ESD

- Selection of an ESD is very important as it introduces a significant impedance discontinuity

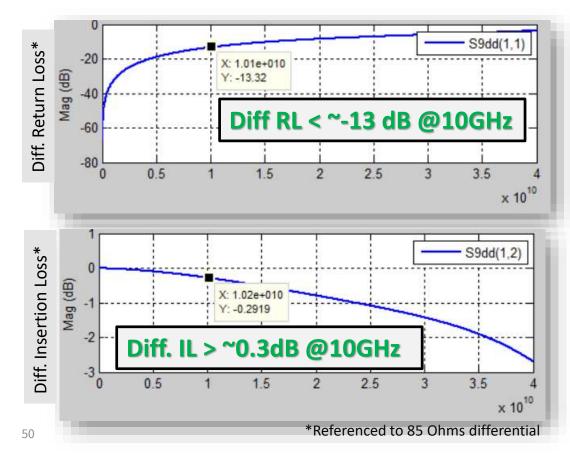

- Recommend using an ESD whose return loss and insertion loss is similar or better than shown below:

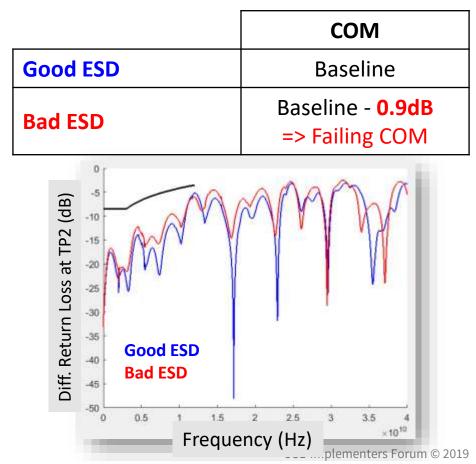

• Example: Impact of a poorly selected ESD: an ESD that fails the RL guideline by ~4.3 dB and the IL by 0.4dB has a large impact to COM and degrades return loss at TP2 when used in short channel

## **PCB** Material

- PCB Thickness: The tradeoff for thinner PCBs (=>thinner dielectric) is higher trace loss

- Example: notice the dependence of loss per inch to dielectric height for a microstrip

| Dielectric height         | 2.7 mils | 2.5  | 2.3  |

|---------------------------|----------|------|------|

| Loss @ 10GHz<br>(dB/inch) | 1.66     | 1.72 | 1.82 |

- **Mitigation options for reducing loss,** especially in thin PCBs:

- PCB material and copper selection

- Optimizing trace geometry (less effective for thin PCBs)

#### • Dielectric Loss

• Low loss and mid loss materials can recover the interconnect reach when using a thin PCB

|                           | Diff. Loss Per Inch |

|---------------------------|---------------------|

| Regular loss (Df = 0.015) | 1.8dB/inch          |

| Mid loss (Df = 0.011)     | 1.6dB/inch          |

| low loss (Df = 0.005 )    | 1.2 dB/inch         |

Example: Stripline w/ D1/D2~=60um

#### Copper Foil Roughness

• At USB4 Gen 3 data rate, copper roughness impacts loss.

| Loss per inch @<br>10GHz | Ultra-<br>smooth | Smooth | Less<br>rough | Very<br>Rough |

|--------------------------|------------------|--------|---------------|---------------|

| Microstrip               | 1.34             | 1.43   | 1.52          | 1.6           |

| Stripline (thin<br>PCB)  | 1.66             | 1.83   | 2             | 2.16          |

#### Summary

- Two categories of channel/interconnect => different design targets/priorities

- Explicit electrical design targets per the USB4 spec

- Loss => |S| => DDJ

- Return loss

- Optimize trace geometry for Impedance, loss, and cross talk

- Routing practices

- Reduce cross talk by interleaved routing

- Avoid via stubs

- Optimize the placement of discrete components (e.g. AC-caps, ESD, etc)

- Layout design guidelines

- Fiberweave effect and mitigation techniques

- Correct values and voltage rating of Rs and Cs

- Choose an ESD with better or equal to the recommended electrical performance

- PCB dielectric material and copper has large impact on trace loss at USB4 data rates

# Time for Q&A

USB Implementers Forum © 2019