# USB 3.1 / USB TYPE-C<sup>TM</sup> DESKTOP FRONT PANEL CABLE AND CONNECTOR IMPLEMENTATION DOCUMENT

Revision 1.1

July 14, 2017

Copyright © 2016 USB Implementers Forum, Inc. All rights reserved.

## Copyright © 2016, USB Implementers Forum, Inc.

## All rights reserved.

#### Legal Disclaimers

A LICENSE IS HEREBY GRANTED TO REPRODUCE THIS DOCUMENT FOR INTERNAL USE ONLY. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, IS GRANTED OR INTENDED HEREBY.

USB-IF AND THE AUTHORS OF THIS DOCUMENT EXPRESSLY DISCLAIM ALL LIABILITY FOR INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS DOCUMENT. USB-IF AND THE AUTHORS OF THIS DOCUMENT ALSO DO NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE THE INTELLECTUAL PROPERTY RIGHTS OF OTHERS.

THIS DOCUMENT IS PROVIDED "AS IS" AND WITH NO WARRANTIES, EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE. ALL WARRANTIES ARE EXPRESSLY DISCLAIMED. NO WARRANTY OF MERCHANTABILITY, NO WARRANTY OF NON-INFRINGEMENT, NO WARRANTY OF FITNESS FOR ANY PARTICULAR PURPOSE, AND NO WARRANTY ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE. THE PROVISION OF THIS DOCUMENT TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

USB Type-C<sup>™</sup> and USB-C<sup>™</sup> are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). All product names are trademarks, registered trademarks, or service marks of their respective owners

## **REVISION HISTORY**

| Date Document Version |          | Revisions              |  |  |  |

|-----------------------|----------|------------------------|--|--|--|

| 01-17-2017            | Rev. 1.0 | First release          |  |  |  |

| July-14-2017          | Rev. 1.1 | Updated Key-B drawings |  |  |  |

# **CONTENTS**

| 1.         | Introduction                                                            | 5  |

|------------|-------------------------------------------------------------------------|----|

| 2.         | Mating Interfaces and Mechanical Requirements                           | 6  |

|            | 2.1 20-Pin Header                                                       |    |

|            | 2.1.1 Mating Interface                                                  |    |

|            | 2.1.2 Reference Footprint                                               |    |

|            | 2.2 40-Pin Header                                                       |    |

|            | 2.2.1 Mating Interface                                                  |    |

|            | 2.2.2 Reference Footprint                                               |    |

|            | 2.3 Important Implementation Notes                                      | 15 |

|            | 2.4 Mechanical Requirements                                             | 17 |

| 3.         | SIGNALS, PIN-OUTS AND WIRING                                            | 18 |

|            | 3.1 Signal Lists                                                        |    |

|            | 3.2 Pin-outs and Wiring                                                 |    |

|            | 3.2.1 Key-A 20-Pin Connector                                            |    |

|            | 3.2.1.1 20-Pin Plug to One USB Type-C Port                              |    |

|            | 3.2.1.2 20-Pin Plug to One Standard-A Port                              |    |

|            | 3.2.2 Key-B 20-Pin Connector                                            |    |

|            | 3.2.3 40-Pin Connector                                                  |    |

|            | 3.2.3.1 40-Pin Connector to Two USB Type-C Ports                        |    |

|            | 3.2.3.2 40-Pin Connector to one USB Type-C Port and one Standard-A Port |    |

|            | 3.2.3.3 40-Pin Connector to two Standard-A Ports                        |    |

| <b>4</b> . | Electrical Requirements                                                 | 27 |

|            | 4.1 Loss Budget                                                         |    |

|            | 4.2 Signal Integrity Requirements                                       |    |

|            | 4.2.1 Raw Cable                                                         |    |

|            | 4.2.2 Mated Connector Impedance                                         |    |

|            | 4.2.3 Mated Cable Assemblies                                            |    |

|            | 4.3 DC Requirements                                                     |    |

|            | 4.3.1 Mated connector current carrying requirements                     |    |

|            | 4.3.2 Cable assembly IR drop requirement                                |    |

## 1. INTRODUCTION

Desktop PC's usually have USB ports on the front-panel of the enclosure and an internal cable assembly is typically used to connect the external USB ports on the front panel to the motherboard.

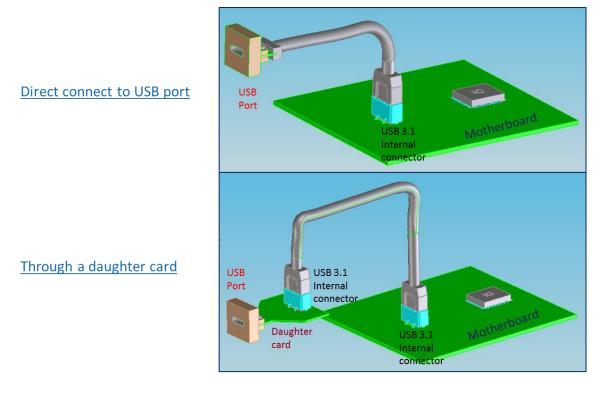

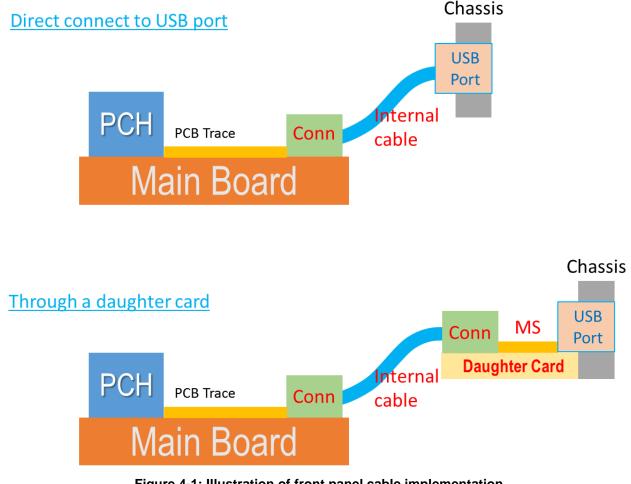

The internal cable assembly may connect the motherboard to the external USB ports via a daughter card, or direct-connect to the external USB ports or receptacle connectors. Figure 1-1 illustrates those two interconnect topologies. A redriver/retimer may be needed on the daughter card in the daughter-card topology, depending on the daughter card design.

#### Figure 1-1: Illustration of USB 3.1 Interconnect Topologies with Internal Cable

The purpose of this document is to help PC manufacturers to implement USB 3.1 Standard-A and USB Type-C connectors for desktop front-panel applications. It provides reference designs of the front panel connectors and cable assemblies, and describes their electrical and mechanical requirements.

This document is not part of the USB base specifications. Implementers may choose to deviate from the defined reference designs, but it is strongly recommended that the electrical requirements specified in this document be followed.

# 2. MATING INTERFACES AND MECHANICAL REQUIREMENTS

The receptacle connector mounted on motherboard (MB) is referred to as the header. To provide configuration flexibility of the USB ports on the front panel, this document defines a 20-pin and a 40-pin header. The 20-pin header has two keying options. The 20-pin header with Key-A supports 1 USB Type-C port or 1 Standard-A port. The 20-pin header with Key-B supports 2 Standard-A ports.

## 2.1 20-Pin Header

## 2.1.1 Mating Interface

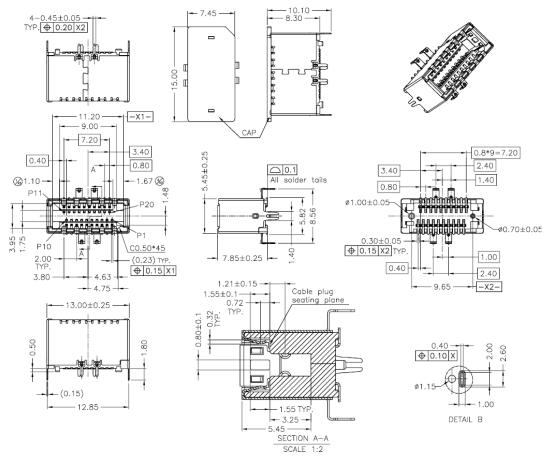

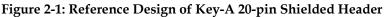

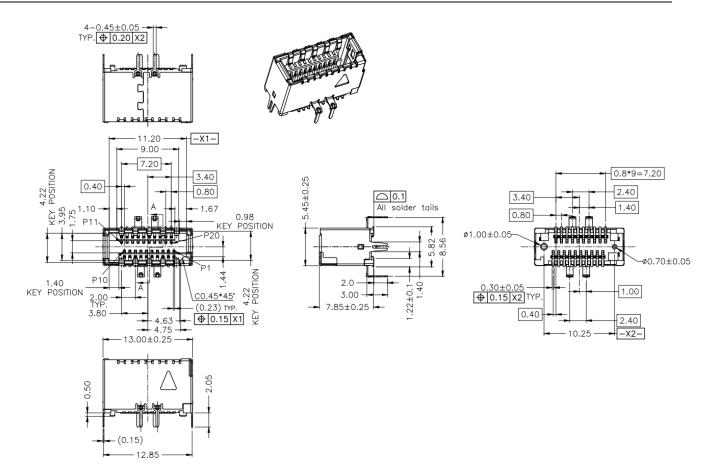

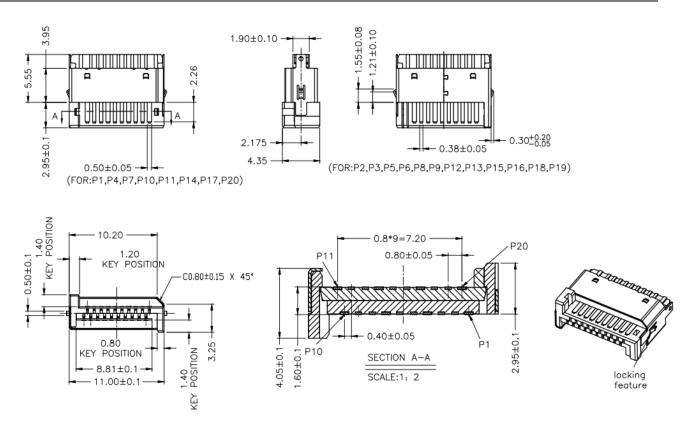

Figure 2-1 shows the reference design of the Key-A 20-pin shielded header, while Figure 2-2 shows the reference design of the Key-A 20-pin unshielded header. The shielded header is to mitigate radio frequency interference (RFI) risk for the systems where RFI is a concern. The unshielded header may be used if the RFI risk is deemed low.

Note: (1) A right-angle header is allowed.

Figure 2-2: Reference Design of Key-A 20-pin Un-shielded Header

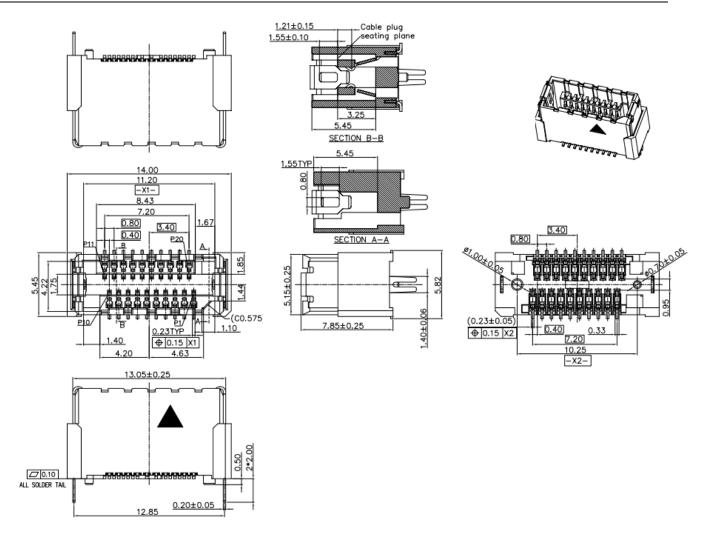

Figure 2-3 shows the reference design of the Key-B 20-pin shielded header, while Figure 2-4 shows the reference design of the Key-B 20-pin unshielded header. The shielded header is to mitigate radio frequency interference (RFI) for the systems where RFI is a concern. The unshielded header may be used if the RFI risk is deemed low.

Figure 2-3: Reference Design of Key-B 20-pin Shielded Header

Figure 2-4: Reference Design of Key-B 20-pin Un-shielded Header

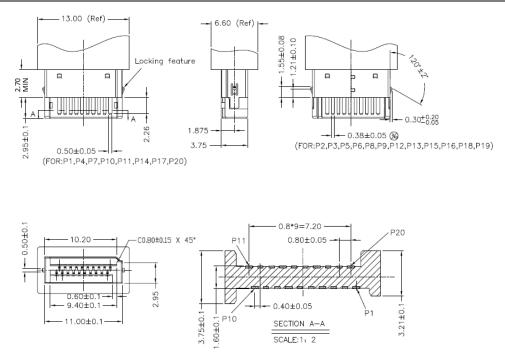

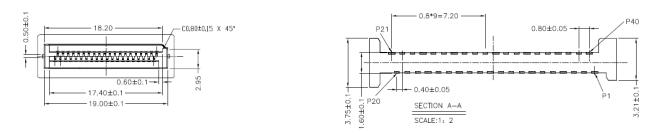

Figure 2-5 shows the reference design of the Key-A 20-pin plug, while Figure 2-6 shows the reference design of the Key-B 20-pin plug. The Key-A plug can only be plugged into the Key-A header. The same is true for the Key-B plug and header.

(2) Metal shell feature (see Figure 2-13) is required to ensure the plug can mate with the shielded header. Figure 2-5: Reference Design of Key-A 20-Pin Cable Plug Interface Dimensions

*Note: (1) A right-angle cable plug is allowed.*

(2) Metal shell feature (see Figure 2-13) is required to ensure the plug can mate with the shielded header. Figure 2-6: Reference Design of Key-B 20-Pin Cable Plug Interface Dimensions

## 2.1.2 Reference Footprint

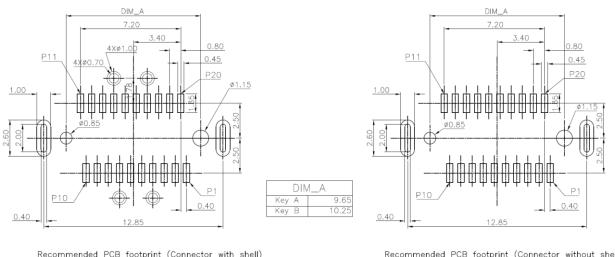

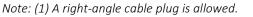

Figure 2-7 shows the reference footprints for the 20-pin headers defined in Section 2.1.1.

Recommended PCB footprint (Connector with shell) All dimensions tolerance is  $\pm 0.05$

Recommended PCB footprint (Connector without shell) All dimensions tolerance is  $\pm 0.05$

#### Figure 2-7: Recommended Footprint for 20-Pin Headers

## 2.2 40-Pin Header

## 2.2.1 Mating Interface

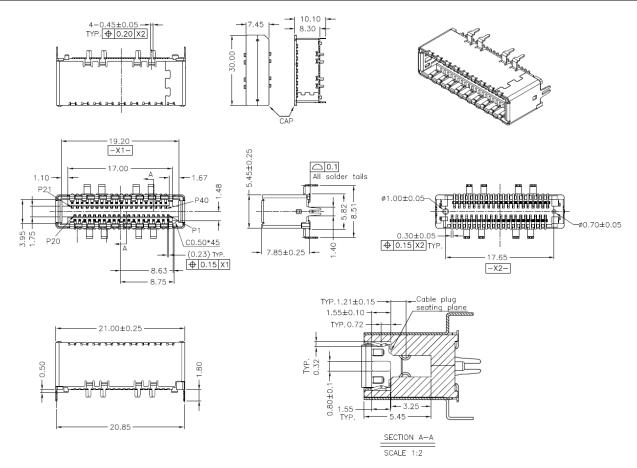

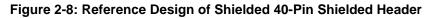

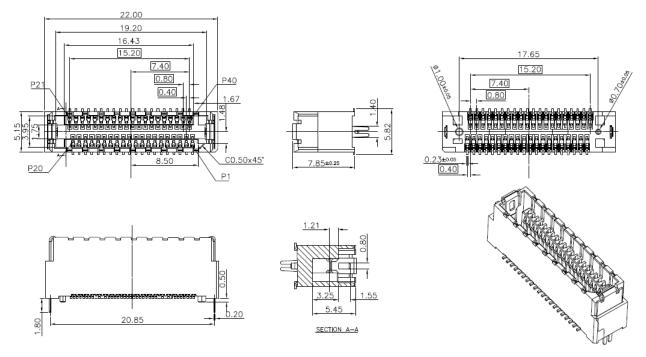

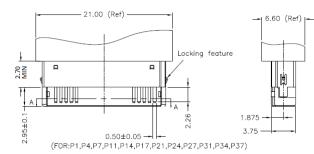

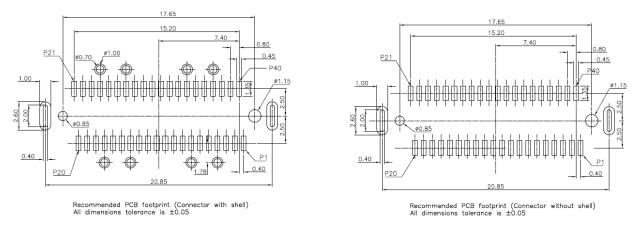

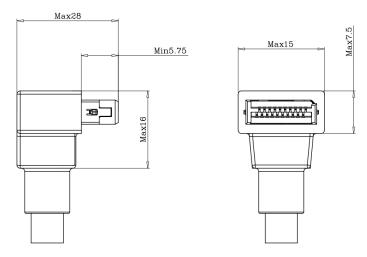

The 40-pin header/plug is a simple extension of the 20-pin header/plug with the only difference being the pin count. Figure 2-8, Figure 2-9 and Figure 2-10 show the 40-pin header and cable plug mating interface dimensions, respectively.

#### Figure 2-9: Reference Design of 40-Pin Unshielded Header

(2) Metal shell feature is required to ensure the plug can mate with the shielded header.

Figure 2-10: Reference Design of 40-Pin Cable Plug

## 2.2.2 Reference Footprint

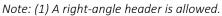

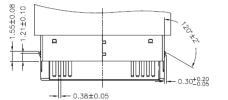

Figure 2-9 shows the reference footprints for the 40-pin headers defined in Section 2.2.1.

Figure 2-11: Recommended Footprints for 40-Pin Headers

## 2.3 Important Implementation Notes

The followings should be noticed:

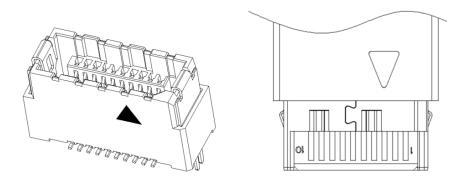

Orientation arrow mark is required on both header and plug. The mark is located in the length direction near pin-3 position. The examples of header arrow mark and plug arrow mark are shown in Figure 2-12

Figure 2-12: Reference Design of alignment arrow marks of header and plug

- 2. To easily differentiate Key-A 20-pin header and Key-B 20-pin header, it is recommended to use black color for Key-A 20-pin header and plug, and use nature or white color for Key-B 20-pin header and plug.

- 3. The reference design is much more compact in size than the USB 3.0 header and therefore more suitable for not only desktops in standard chassis but also smaller form factors.

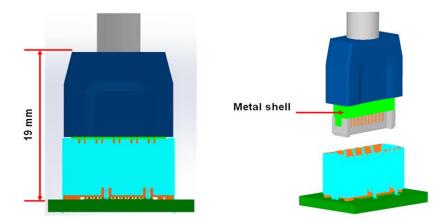

- 4. The mated connector is illustrated in Figure 2-13. A right-angle plug may be used. Note that the 19 mm dimension represents the minimum height that may be achieved in one implementation. In general, the mated height may be larger than this. Please check with cable/connector vendors on this dimension.

Figure 2-13: Reference Dimensions of Mated Header and Plug

5. The overmold dimensions for a right angle plug are provided below for reference only.

Figure 2-14: Reference Dimensions of Overmold

- 6. The shielded header is wrapped with metal shell around the connector housing. There are multiple grounding fingers on both side, formed in the metal shell to mate with the plug shell when the plug is inserted. The shell should provide sufficient connections to the motherboard ground plane through SMT pads or Through-holes.

- 7. The shielded header may be necessary when the desktop has wireless antenna inside of the enclosure near the USB 3.1 signals and RFI is of a concern. In applications where RFI is not a major concern, unshielded solutions may be used. System OEMs decide this.

- 8. If RFI is a major concern, a fully shielded plug design may be used. For shielding to be effective, the plug shell should reserve sufficient flat surfaces to mate with the grounding fingers on the header. On the wire termination area, the plug shell should be terminated with the cable shielding braid as close to 360-degree as possible.

- 9. In applications where RFI is not deemed to be a major concern, the unshielded plug may be used. But the plug is required to implement metal shell in the mating area (see Figure 2-13) for reliability concern when mating with the shielded header.

- 10. The retention features, one at each end of the header, are stamped and formed in the metal shell to lock the plug in place after the plug is inserted.

- 11. Refer to Chapter 3 for reference pin-out and wiring.

## 2.4 Mechanical Requirements

This document does not specify all the mechanical and reliability requirements. Only the base-line requirements are specified, as defined in Table 2-1 and Table 2-2. It is up to connector vendors and PC manufacturers to decide if additional mechanical requirements are needed.

| Parameter                               | Procedure                                                                                                                 | Requirements                                                         |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Mating<br>force                         | EIA 364-13<br>Measure the force necessary to mate<br>the connector<br>assemblies at a max rate of 12.5 mm<br>per minute.  | 35 N max (20-pin header/plug)<br>40 N max (40-pin header/plug)       |

| Unmating<br>force                       | EIA 364-13<br>Measure the force necessary to un-<br>mate the connector assemblies at a<br>max rate of 12.5 mm per minute. | 15 N min                                                             |

| Durability                              | EIA 364-09<br>50 cycles. Done at a max rate of 200<br>cycles per hour.                                                    | No physical damage to any part of the connector and cable assembly.  |

| Cable<br>flexing                        | EIA 364-41 Condition I<br>Dimension X=5.5x cable diameter. 50<br>cycles in each of two planes                             | No physical damage. No<br>discontinuity over 1 ms during<br>flexing. |

| Visual and<br>dimensional<br>inspection | EIA 364- 18<br>Visual, dimensional and functional<br>inspection per applicable quality<br>inspection plan.                | Meets product drawing requirements                                   |

Table 2-1 Cable Assembly Mechanical Requirements

Special attention shall be paid to the unmating force. Since there is no positive retention mechanism defined for the cable assembly, the unmating force between the cable plug and header is the only mechanism to retain the cable assembly during shock and vibration.

The mated cable assembly shall pass the system level shock and vibration tests. The table below specifies the baseline shock and vibration requirements. Variation from those baseline requirements is allowed at each OEM's discretion.

| Test Name                                | Procedure                                                                                                                                                                                                                            | Requirements                                                                                                                                                                                                             |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tem level<br>Shock,<br>unpackaged        | 30G trapezoidal, 170 in/second; 3 drops in each of the 6 axes.                                                                                                                                                                       | No visible damage.<br>No displacement of components,<br>cable, or hardware.<br>The product must operate normally<br>after the completion of the stress.                                                                  |

| System level<br>vibration,<br>unpackaged | Random profile: 5 Hz @ 0.001 g <sup>2</sup> / Hz<br>to 20 Hz @ 0.01 g <sup>2</sup> /Hz (slope up); 20<br>Hz to 500 Hz @ 0.01 g <sup>2</sup> / Hz (flat).<br>Input acceleration is 2.20 g RMS. 10<br>minutes per axis for all 3 axes. | No visible damage.<br>No displacement of the cable<br>interface.<br>No more than one intermittent failure<br>during random vibration stress.<br>The product must operate normally<br>after the completion of the stress. |

Table 2-2 Cable Assembly Shock and Vibration Requirements

# 3. SIGNALS, PIN-OUTS AND WIRING

## 3.1 Signal Lists

The signals required by the Standard-A and USB Type-C connectors shall be supported. Table 3-1 and Table 3-2 show the signals required by the USB Standard-A and USB Type-C connectors, respectively. Supporting of other signals is implementation- specific and not covered in this document.

| Signal Name               | Description                              | Note                                |

|---------------------------|------------------------------------------|-------------------------------------|

| VBUS                      | Power                                    |                                     |

| D-/D+                     | USB 2.0 differential pair                |                                     |

| GND                       | Ground for power return                  |                                     |

| StdA_SSRX-,<br>StdA_SSRX+ | SuperSpeed receiver differential pair    | Rx is defined from host perspective |

| GND_DRAIN                 | Ground for signal return                 |                                     |

| StdA_SSTX-,<br>StdA_SSTX+ | SuperSpeed transmitter differential pair | Tx is defined from host perspective |

| Table 3-1: Signals in USB 3.1 Sta | ndard-A Connector |

|-----------------------------------|-------------------|

|-----------------------------------|-------------------|

Note: Refer to USB 3.1 Specification for more detail.

| Table 3-2: Signals in USB | <b>Type-C Connector</b> | (Full-Featured) |

|---------------------------|-------------------------|-----------------|

|---------------------------|-------------------------|-----------------|

| Signal Name | Description | Note |

|-------------|-------------|------|

| VBUS        | BUS power   |      |

| GND               | Ground return                              |                                     |

|-------------------|--------------------------------------------|-------------------------------------|

| Dn/Dp             | USB 2.0 differential pair                  |                                     |

| SSRXn1,<br>SSRXp1 | SuperSpeed receiver differential pair 1    | Rx is defined from host perspective |

| SSTXn1,<br>SSTXp1 | SuperSpeed transmitter differential pair 1 | Tx is defined from host perspective |

| SSRXn2,<br>SSRXp2 | SuperSpeed receiver differential pair 2    | Rx is defined from host perspective |

| SSTXn2,<br>STRXp2 | SuperSpeed transmitter differential pair 2 | Tx is defined from host perspective |

| CC1               | Configuration Channel                      |                                     |

| CC2               | Configuration Channel                      | Named VCONN on the plug side        |

| SBU1              | Sideband Use (SBU)                         |                                     |

| SBU2              | Sideband Use (SBU)                         |                                     |

Note: Refer to USB Type-C Specification for more detail.

## 3.2 Pin-outs and Wiring

The mechanical definitions of the 20-pin and 40-pin connectors are discussed in Sections 2.1 and 2.2, respectively. Note that all internal cables defined are not reversible or flip-able. It should also be noted that the reference designs do not support the reconfiguration of pins B6 and B7 for Direct Connect Alternate Mode applications and Debug Accessory Modes – see USB Type-C Specification.

## 3.2.1 Key-A 20-Pin Connector

### 3.2.1.1 20-Pin Plug to One USB Type-C Port

The pin assignment or pin-out shown Figure 3-1 is to support one USB Type-C port, looking into the front of the header.

| P1   | P2   | P3   | P4  | P5   | P6   | P7   | P8   | Р9   | P10  |

|------|------|------|-----|------|------|------|------|------|------|

| VBUS | TX1+ | TX1- | GND | RX1+ | RX1- | VBUS | CC1  | SBU1 | SBU2 |

|      |      |      |     |      |      |      |      |      |      |

| CC2  | D+   | D-   | GND | RX2- | RX2+ | GND  | TX2- | TX2+ | VBUS |

| P20  | P19  | P18  | P17 | P16  | P15  | P14  | P13  | P12  | P11  |

#### Figure 3-1: Pin-out of 20-Pin Header with One USB Type-C Port

The wire connections are shown in Table 3-3. The pin numbers for the USB Type-C receptacle are defined in the *USB Type-C Specification*. Table 3-3 is based on the assumption that shielded twisted pair is used for all SDP's (shielded differential pairs) and there are drain wires used. If coaxial wire construction is used, then no drain wires are present and the shields of the coaxial wires are connected to the ground pins via a ground bar.

| Header Side Plug |                | Wire                                                                   | Type-C Receptacle |             |  |

|------------------|----------------|------------------------------------------------------------------------|-------------------|-------------|--|

| Pin              | Signal<br>Name | Signal Name                                                            | Pin               | Signal Name |  |

| P4,P14,P17       | GND            | GND_PWRrt1 [GND_PWRrt2]<br>GND_drain1 to GND_drain4 A1, B1, A12, B12 G |                   | GND         |  |

| P1,P7,P11        | VBUS           | PWR_VBUS1 [PWR_VBUS2]                                                  | A4, B4, A9, B9    | VBUS        |  |

| P2               | SSTXp1         | SDPp1                                                                  | A2                | SSTXp1      |  |

| P3               | SSTXn1         | SDPn1                                                                  | A3                | SSTXn1      |  |

| P5               | SSRXp1         | SDPp2                                                                  | 811               | SSRXp1      |  |

| P6               | SSRXn1         | SDPn2                                                                  | B10               | SSRXn1      |  |

| P12              | SSTXp2         | SDPp3                                                                  | B2                | SSTXp2      |  |

| P13              | SSTXn2         | SDPn3                                                                  | B3                | SSTXn2      |  |

| P15              | SSRXp2         | SDPp4                                                                  | A11               | SSRXp2      |  |

| P16              | SSRXn2         | SDPn4                                                                  | A10               | SSRXn2      |  |

| P8               | CC1            | CC1                                                                    | A5                | CC1         |  |

| P9               | SBU1           | SBU_A                                                                  | A8                | SBU1        |  |

| P10              | SBU2           | SBU_B                                                                  | 88                | SBU2        |  |

| P18              | Dn             | UTP_Dn                                                                 | A7                | Dn1         |  |

| P19              | Dp             | UTP_Dp                                                                 | A6                | Dp1         |  |

| P20              | CC2            | CC2                                                                    | 85                | CC2         |  |

| Shell            | Shield         | Shield (Cable external braid)                                          | Shell             | Shield      |  |

Table 3-3: Cable Assembly Wiring for 20-Pin Plug to One USB Type-C Port

Note: (1) GND\_PWRrt is the ground pins used for current return for power pins. At least one ground wire for power return current is required, but multiple ground wires for power return are allowed.

(2) A SDP (Shielded Differential Pair) typically has a drain wire that should be soldered to ground pins. GND\_drain1 to GND\_drain4 means drain wire number 1 to 4, respectively.

(3) Pin B6 on the USB Type-C side shall be shorted with pin A6 (on paddle card) and Pin B7 shall be shorted with pin A7 (on paddle card), as close to the USB Type-C receptacle contacts as possible. Refer to USB Type-C Specification for more detail.

### 3.2.1.2 20-Pin Plug to One Standard-A Port

If the same pin-out defined in Figure 3-1 is used to support one Standard-A port, only a subset of the pins will be used, as marked in Figure 3-2 below

| P1   | P2   | Р3   | P4  | P5   | P6   | Ρ7   | P8  | P9  | P10  |

|------|------|------|-----|------|------|------|-----|-----|------|

| VBUS | TX1+ | TX1- | GND | RX1+ | RX1- | VBUS | CC1 |     |      |

|      |      |      |     |      |      |      |     |     |      |

|      | D+   | D-   | GND |      |      | GND  |     |     | VBUS |

| P20  | P19  | P18  | P17 | P16  | P15  | P14  | P13 | P12 | P11  |

Figure 3-2: Pin-out of 20-Pin Connector for Supporting One Standard-A Port

The wire connections are shown in Table 3-4. The pin numbers of the Standard-A receptacle are defined in the *USB 3.1 Specification*. Table 3-4 is based on the assumption that shielded twisted pairs are used for all SDP's and

there are drain wires used. If coaxial wire construction is used, then no drain wires are present and the shields of the coaxial wires are connected to the ground pins via a ground bar.

| Header Si | ide Plug       | Wire                          | Standrd A Receptacle |             |  |

|-----------|----------------|-------------------------------|----------------------|-------------|--|

| Pin       | Signal<br>Name | Signal Name                   | Pin                  | Signal Name |  |

| P1,P7,P11 | VBUS           | PWR_VBUS                      | Std-A-1              | VBUS        |  |

| P2        | SSTXp1         | SDPp1                         | Std-A-9              | SSTXp       |  |

| P3        | SSTXn1         | SDPn1                         | Std-A-8              | SSTXn       |  |

| P4        | GND            | GND_drain                     | Std-A-7              | GND         |  |

| P5        | SSRXp1         | SDPp1                         | Std-A-6              | SSRXp       |  |

| P6        | SSRXn1         | SDPn1                         | Std-A-5              | SSRXn       |  |

| P14, P17  | GND            | GND_PWRrt                     | Std-A-4              | GND         |  |

| P18       | Dn             | UTP_Dn                        | Std-A-2              | Dn1         |  |

| P19       | Dp             | UTP_Dp                        | Std-A-3              | Dp1         |  |

| Shell     | Shield         | Shield (Cable external braid) | Shell                | Shield      |  |

Table 3-4: Cable Assembly Wiring for 20-Pin Plug to One Standard-A Port

Note that Pin 8 (CC1) of the header plug shall be terminated with an Rd= 5.1 kOhms +/- 20% resistor to ground. This will allow a common motherboard design to support either a USB Type-C or a Standard-A port on the front panel for the DIY (do-it-yourself) market.

## 3.2.2 Key-B 20-Pin Connector

The pin assignment shown Figure 3-3 is to support two Standard-A ports, looking into the front of the header.

| P1   | P2   | Р3   | P4  | P5   | P6   | P7  | P8   | P9   | P10  |

|------|------|------|-----|------|------|-----|------|------|------|

| GND  | TX1+ | TX1- | GND | RX1+ | RX1- | GND | D1+  | D1-  | VBUS |

|      |      |      |     |      |      |     |      |      |      |

| VBUS | D2-  | D2+  | GND | RX2+ | RX2- | GND | TX2+ | TX2- | GND  |

|      |      |      |     |      |      |     |      |      |      |

Figure 3-3: Pin-out of 20-Pin Header for Two Standard-A Ports

The wire connections are shown in Table 3-5. Note that Table 3-5 assumes direct connect to the USB Standard-A port. The pin numbers of the Standard-A receptacle are defined in the *USB 3.1 Specification*.

Table 3-5 is based on the assumption that shielded twisted pairs are used for all SDP's and there are drain wires used. If coaxial wire construction is used, then no drain wires are present and the shields of the coaxial wires are connected to the ground pins via a ground bar.

For an unshielded cable assembly, plug shells at both sides and cable external braid are removed from Table 3-5.

| Header S | ide Plug       | Wire                          | (Two) Standa | rd A Receptacles |

|----------|----------------|-------------------------------|--------------|------------------|

| Pin      | Signal<br>Name | Signal Name                   | Pin          | Signal Name      |

| P1       | GND            | GND_drain1                    | Std-A1-7     | GND              |

| P2       | SSTXp1         | SDPp1                         | Std-A1-9     | SSTXp1           |

| РЗ       | SSTXn1         | SDPn1                         | Std-A1-8     | SSTXn1           |

| P4       | GND            | GND_drain2                    | Std-A1-7     | GND              |

| Р5       | SSRXp1         | SDPp2                         | Std-A1-6     | SSRXp1           |

| P6       | SSRXn1         | SDPn2                         | Std-A1-5     | SSRXn1           |

| Р7       | GND            | GND_PWRrt1                    | Std-A1-4     | GND              |

| P8       | Dp1            | UTP_Dn1                       | Std-A1-3     | Dp1              |

| Р9       | Dn1            | UTP_Dp1                       | Std-A1-2     | Dn1              |

| P10      | VBUS           | PWR_VBUS1                     | Std-A1-1     | VBUS             |

| P11      | GND            | GND_drain3                    | Std-A2-7     | GND              |

| P12      | SSTXn2         | SDPn3                         | Std-A2-9     | SSTXn2           |

| P13      | SSTXp2         | SDPp3                         | Std-A2-8     | SSTXp2           |

| P14      | GND            | GND_drain4                    | Std-A2-7     | GND              |

| P15      | SSRXn2         | SDPn4                         | Std-A2-6     | SSRXn2           |

| P16      | SSRXp2         | SDPp4                         | Std-A2-5     | SSRXp2           |

| P17      | GND            | GND_PWRrt2                    | Std-A2-4     | GND              |

| P18      | Dp2            | UTP_Dp2                       | Std-A2-3     | Dp2              |

| P19      | Dn2            | UTP_Dn2                       | Std-A2-2     | Dn2              |

| P20      | VBUS           | PWR_VBUS2                     | Std-A2-1     | VBUS             |

| Shell    | Shield         | Shield (Cable external braid) | Shell        | Shield           |

*Note: (1) GND\_PWRrt means the ground pins used for current return for power pins.*

(2) A SDP (Shielded Differential Pair) cable typically has a drain wire that should be soldered to ground pins. GND\_drain1 to GND\_drain4 means number 1 to 4 of drain wires used in SDP, respectively.

## 3.2.3 40-Pin Connector

#### 3.2.3.1 40-Pin Connector to Two USB Type-C Ports

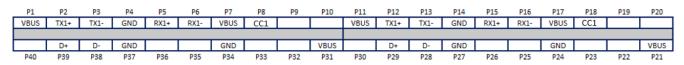

The pin assignment or pin-out shown in Figure 3-4 is to support two USB Type-C ports, looking into the front of the header.

| P1   | P2   | P3   | P4  | P5   | P6   | P7   | P8   | P9   | P10  | P11  | P12  | P13  | P14 | P15  | P16  | P17  | P18  | P19  | P20  |

|------|------|------|-----|------|------|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|

| VBUS | TX1+ | TX1- | GND | RX1+ | RX1- | VBUS | CC1  | SBU1 | SBU2 | VBUS | TX1+ | TX1- | GND | RX1+ | RX1- | VBUS | CC1  | SBU1 | SBU2 |

|      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |

|      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |

| CC2  | D+   | D-   | GND | RX2- | RX2+ | GND  | TX2- | TX2+ | VBUS | CC2  | D+   | D-   | GND | RX2- | RX2+ | GND  | TX2- | TX2+ | VBUS |

#### Figure 3-4: Pin-out of 40-Pin Connector for Supporting Two USB Type-C Ports

The wire connections are shown in Table 3-6, which assumes direct-connect to the USB Type-C ports. The pin numbers are defined in *USB Type-C Specification*.

Table 3-6 is based on the assumption that shielded twisted pair is used for all SDP's and there are drain wires used. If coaxial wire construction is used, no drain wires are present and the shields of the coaxial wires are connected to the ground pins via a ground bar.

| Header Sid  | le Plug        | Wire                                                | (Two) Type-C I   | Receptacles |

|-------------|----------------|-----------------------------------------------------|------------------|-------------|

| Pin         | Signal<br>Name | Signal Name                                         | Pin              | Signal Name |

| P4,P34,P37  | GND            | GND_PWRrt1 [GND_PWRrt2]<br>GND_drain1 to GND_drain4 | A1, B1, A12, B12 | GND         |

| P1,P7,P31   | VBUS           | PWR_VBUS1 [PWR_VBUS2]                               | A4, B4, A9, B9   | VBUS        |

| P2          | SSTXp1         | SDPp1                                               | A2               | SSTXp1      |

| P3          | SSTXn1         | SDPn1                                               | A3               | SSTXn1      |

| P5          | SSRXp1         | SDPp2                                               | 811              | SSRXp1      |

| P6          | SSRXn1         | SDPn2                                               | B10              | SSRXn1      |

| P32         | SSTXp2         | SDPp3                                               | B2               | SSTXp2      |

| P33         | SSTXn2         | SDPn3                                               | 83               | SSTXn2      |

| P35         | SSRXp2         | SDPp4                                               | A11              | SSRXp2      |

| P36         | SSRXn2         | SDPn4                                               | A10              | SSRXn2      |

| P8          | CC1            | CC1_1                                               | A5               | CC1         |

| P9          | SBU1           | SBU_1A                                              | A8               | SBU1        |

| P10         | SBU2           | SBU_1B                                              | B8               | SBU2        |

| P38         | Dn             | UTP_Dn1                                             | A7               | Dn1         |

| P39         | Dp             | UTP_Dp1                                             | A6               | Dp1         |

| P40         | CC2            | CC2_1                                               | 85               | CC2         |

| P14,P24,P27 | GND            | GND_PWRrt3 [GND_PWRrt4]<br>GND_drain5 to GND_drain8 | A1, B1, A12, B12 | GND         |

| P11,P17,P21 | VBUS           | PWR_VBUS3 [PWR_VBUS4]                               | A4, B4, A9, B9   | VBUS        |

| P12         | SSTXp1         | SDPp5                                               | A2               | SSTXp1      |

| P13         | SSTXn1         | SDPn5                                               | A3               | SSTXn1      |

| P15         | SSRXp1         | SDPp6                                               | B11              | SSRXp1      |

| P16         | SSRXn1         | SDPn6                                               | B10              | SSRXn1      |

| P22         | SSTXp2         | SDPp7                                               | B2               | SSTXp2      |

| P23         | SSTXn2         | SDPn7                                               | 83               | SSTXn2      |

| P25         | SSRXp2         | SDPp8                                               | A11              | SSRXp2      |

| P26         | SSRXn2         | SDPn8                                               | A10              | SSRXn2      |

| P18         | CC1            | CC1_2                                               | A5               | CC1         |

| P19         | SBU1           | SBU_2A                                              | A8               | SBU1        |

| P20         | SBU2           | SBU_2B                                              | 88               | SBU2        |

| P28         | Dn             | UTP_Dn2                                             | A7               | Dn1         |

| P29         | Dp             | UTP_Dp2                                             | A6               | Dp1         |

| P30         | CC2            | CC2_2                                               | 85               | CC2         |

| Shell       | Shield         | Shield (Cable external braid)                       | Shell            | Shield      |

Table 3-6: Cable Assembly Wiring for 40-Pin ICC to 2 USB Type-C Ports

(2) GND\_PWRrt means the ground pins used for current return for power pins. At least one ground wire for power return current is required, but  $2^{nd}$  ground wire for power return is allowed.

Note: (1) Pin B6 on the USB Type-C side shall be shorted with pin A6 (on paddle card) and Pin B7 shall be shorted with pin A7 (on paddle card), as close to the USB Type-C receptacle contacts as possible. Refer to USB Type-C Specification for more detail.

(3) An SDP (Shielded Differential Pair) cable typically has a drain wire that should be soldered to ground pins. GND\_drain1 to GND\_drain8 means number 1 to 8 of drain wires used in SDP, respectively.

#### 3.2.3.2 40-Pin Connector to one USB Type-C Port and one Standard-A Port

To support one USB Type-C port and one Standard-A port, only a subset of pins in Figure 3-5 will be used:

| P1   | P2   | P3   | P4  | <b>P</b> 5 | P6   | P7   | P8   | P9   | P10  | P11  | P12  | P13  | P14 | P15  | P16  | P17  | P18 | P19 | P20  |

|------|------|------|-----|------------|------|------|------|------|------|------|------|------|-----|------|------|------|-----|-----|------|

| VBUS | TX1+ | TX1- | GND | RX1+       | RX1- | VBUS | CC1  | SBU1 | SBU2 | VBUS | TX1+ | TX1- | GND | RX1+ | RX1- | VBUS | CC1 |     |      |

|      |      |      |     |            |      |      |      |      |      |      |      |      |     |      |      |      |     |     |      |

|      |      |      |     |            |      |      |      |      |      |      |      |      |     |      |      |      |     |     |      |

| CC2  | D+   | D-   | GND | RX2-       | RX2+ | GND  | TX2- | TX2+ | VBUS |      | D+   | D-   | GND |      |      | GND  |     |     | VBUS |

#### Figure 3-5: Header Pins for one USB Type-C port and Standard-A port

The wire connections are shown in Table 3-7, which assumes direct-connect to the USB Type-C and Standard-A ports. Table 3-7 is based on the assumption that shielded twisted pair is used for all SDP's and there are drain wires used. If coaxial wire construction is used, no drain wires are present and the shields of the coaxial wires are connected to the ground pins via a ground bar.

| Header Side<br>Plug |        | Wire                                                |                   | ceptacles and one<br>A recpetable |  |

|---------------------|--------|-----------------------------------------------------|-------------------|-----------------------------------|--|

| Pin Signal Name     |        | Signal Name                                         | Pin               | Signal Name                       |  |

| P4,P34,P37          | GND    | GND_PWRrt1 [GND_PWRrt2]<br>GND_drain1 to GND_drain4 | A1, B1, A12, B12  | GND                               |  |

| P1,P7,P31           | VBUS   | PWR_VBUS1 [PWR_VBUS2]                               | A4, B4, A9, B9    | VBUS                              |  |

| P2                  | SSTXp1 | SDPp1                                               | A2                | SSTXp1                            |  |

| P3                  | SSTXn1 | SDPn1                                               | A3                | SSTXn1                            |  |

| P5                  | SSRXp1 | SDPp2                                               | B11               | SSRXp1                            |  |

| P6                  | SSRXn1 | SDPn2                                               | B10               | SSRXn1                            |  |

| P32                 | SSTXp2 | SDPp3                                               | B2                | SSTXp2                            |  |

| P33                 | SSTXn2 | SDPn3                                               | B3                | SSTXn2                            |  |

| P35                 | SSRXp2 | SDPp4                                               | A11               | SSRXp2                            |  |

| P36                 | SSRXn2 | SDPn4                                               | A10               | SSRXn2                            |  |

| P8                  | CC1    | CC1                                                 | A5                | CC1                               |  |

| P9                  | SBU1   | SBU_1A                                              | A8                | SBU1                              |  |

| P10                 | SBU2   | SBU_1B                                              | B8                | SBU2                              |  |

| P38                 | Dn     | UTP_Dn1                                             | A7                | Dn1                               |  |

| P39                 | Dp     | UTP_Dp1                                             | A6                | Dp1                               |  |

| P40                 | CC2    | CC2                                                 | B5                | CC2                               |  |

| P14,P24,P27         | GND    | GND_PWRrt3 [GND_PWRrt4]<br>GND_drain5 to GND_drain8 | Std-A-4 / Std-A-7 | GND                               |  |

| P11,P17,P21         | VBUS   | PWR_VBUS3 [PWR_VBUS4]                               | Std-A-1           | VBUS                              |  |

| P12                 | SSTXp1 | SDPp5                                               | Std-A-9           | SSTXp1                            |  |

| P13                 | SSTXn1 | SDPn5                                               | Std-A-8           | SSTXn1                            |  |

| P15                 | SSRXp1 | SDPp6                                               | Std-A-6           | SSRXp1                            |  |

| P16                 | SSRXn1 | SDPn6                                               | Std-A-5           | SSRXn1                            |  |

| P28                 | Dn     | UTP_Dn2                                             | Std-A-2           | Dn1                               |  |

| P29                 | Dp     | UTP_Dp2                                             | Std-A-3           | Dp1                               |  |

| Shell               | Shield | Shield (Cable external braid)                       | Shell             | Shield                            |  |

Table 3-7: Cable Assembly Wiring for 40-Pin ICC to 1 USB Type-C Port and 1 Standard-A Port

Notes: (1) Pin B6 on the USB Type-C side shall be shorted with pin A6 (on paddle card) and Pin B7 shall be shorted with pin A7 (on paddle card), as close to the USB Type-C receptacle contacts as possible. Refer to USB Type-C Specification for more detail.

(2) GND\_PWRrt means the ground pins used for current return for power pins. At least one ground wire for power return current is required, but  $2^{nd}$  ground wire for power return is allowed.

(3) A SDP (Shielded Differential Pair) cable typically has a drain wire that should be soldered to ground pins. GND\_drain1 to GND\_drain8 means number 1 to 8 of drain wires used in SDP, respectively.

(4) Pin18 (CC1) on the header plug is terminated with 5.1 kOhms +/- 20% resistor to ground.

#### 3.2.3.3 40-Pin Connector to two Standard-A Ports

To support two Standard-A ports only, the following pins will be used.

#### Figure 3-6: Pins for Two Standard-A ports

The wire connections are shown in Table 3-8, which assumes direct-connect to the Standard-A ports.

#### Table 3-8: Cable Assembly Wiring for 40-Pin ICC to two Standard-A Ports

| Header Sid  | le Plug        | Wire                                                | (Two) Standard    | A Receptacles |

|-------------|----------------|-----------------------------------------------------|-------------------|---------------|

| Pin         | Signal<br>Name | Signal Name                                         | Pin               | Signal Name   |

| P4,P34,P37  | GND            | GND_PWRrt1 [GND_PWRrt2]<br>GND_drain1 to GND_drain4 | Std-A1-4/Std-A1-7 | GND           |

| P1,P7,P31   | VBUS           | PWR_VBUS1 [PWR_VBUS2]                               | Std-A1-1          | VBUS          |

| P2          | SSTXp1         | SDPp1                                               | Std-A1-9          | SSTXp1        |

| P3          | SSTXn1         | SDPn1                                               | Std-A1-8          | SSTXn1        |

| P5          | SSRXp1         | SDPp2                                               | Std-A1-6          | SSRXp1        |

| P6          | SSRXn1         | SDPn2                                               | Std-A1-5          | SSRXn1        |

| P38         | Dn             | UTP_Dn1                                             | Std-A1-3          | Dn1           |

| P39         | Dp             | UTP_Dp1                                             | Std-A1-2          | Dp1           |

| P14,P24,P27 | GND            | GND_PWRrt3 [GND_PWRrt4]<br>GND_drain5 to GND_drain8 | Std-A2-4/Std-A2-7 | GND           |

| P11,P17,P21 | VBUS           | PWR_VBUS3 [PWR_VBUS4]                               | Std-A2-1          | VBUS          |

| P12         | SSTXp1         | SDPp5                                               | Std-A2-9          | SSTXp1        |

| P13         | SSTXn1         | SDPn5                                               | Std-A2-8          | SSTXn1        |

| P15         | SSRXp1         | SDPp6                                               | Std-A2-6          | SSRXp1        |

| P16         | SSRXn1         | SDPn6                                               | Std-A2-5          | SSRXn1        |

| P28         | Dn             | UTP_Dn2                                             | Std-A2-3          | Dn1           |

| P29         | Dp             | UTP_Dp2                                             | Std-A2-2          | Dp1           |

| Shell       | Shield         | Shield (Cable external braid)                       | Shell             | Shield        |

Note: (1) GND\_PWRrt means the ground pins used for current return for power pins. At least one ground wire for power return current is required, but 2<sup>nd</sup> ground wire for power return is allowed.

(2) A SDP (Shielded Differential Pair) cable typically has a drain wire that should be soldered to ground pins. GND\_drain1 to GND\_drain8 means number 1 to 8 of drain wires used in SDP, respectively.

(3) *Pin8* (CC1) and *Pin18* (CC1) on the header plug are separately terminated with 5.1 kOhms +/- 20% resistor to ground wires.

Note that the pinout and wiring definitions in Section 3.2.2 assume a common motherboard design to support multiple front panel port configurations: 2 USB Type-C ports, one USB Type-C port and one Standard-A port, or two Standard-A ports. For systems that are designed for specific front-panel port configurations, the 40-pin connector may pinned out differently. System OEMs can work with connector vendors to develop desired solutions.

## 4. ELECTRICAL REQUIREMENTS

This chapter describes the loss budget and other electrical requirements.

## 4.1 Loss Budget

For USB 3.1 Gen 2 signals (10 Gbps), the cable assembly loss shall be controlled to ensure the end-to-end channel function properly.

The target differential insertion loss budget of the cable assembly shall be within -3.3 dB at 5 GHz, and the total PCB trace routing length between IC package and the header is recommended to be within 3.5 inches, as small as practically allowed.

Figure 4-1 illustrates two typical interconnect topologies; one is direct-connect-to-USB-ports, and the other uses a daughter card to bridge internal cable to USB ports.

Figure 4-1: Illustration of front panel cable implementation

Based on the total loss budget of -3.3 dB @ 5 GHz, the maximum cable length is estimated in Table 4-9 for reference.

| Cable Types | Structure | Length |

|-------------|-----------|--------|

|             | 28 AWG    | 23     |

|             | 30 AWG    | 18     |

| SDP         | 32 AWG    | 16     |

|             | 34 AWG    | 13     |

|             | 28 AWG    | 23     |

| Coaxial     | 30 AWG    | 18     |

| Cable       | 32 AWG    | 15     |

|             | 34 AWG    | 12     |

#### Table 4-9: Estimated Maximum Direct Connect to USB Port Cable Length (Unit: inch)

There will be additional PCB traces and connectors for the daughter card implementation and it is extremely difficult to meet the loss and other electrical requirement using the daughter card. Therefore, direct-connect to USB Type-C or standard-A receptacle is strongly recommended. If the daughter card implementation has to be used, the whole signal path from the header footprint to the USB receptacle must meet the loss and other electrical requirements defined in this chapter; or a redriver/retime should be used.

## 4.2 Signal Integrity Requirements

## 4.2.1 Raw Cable

There is no raw cable electrical performance specified. Reference USB 3.1 and USB Type-C specifications for raw cable recommendations.

## 4.2.2 Mated Connector Impedance

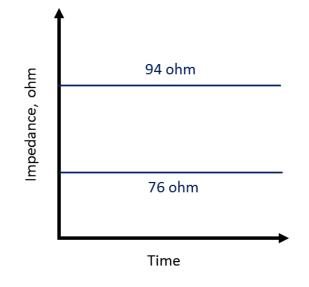

The differential impedance of a mated connector should be  $85 \Omega + /-9 \Omega$ , as seen from a 40-ps (20%-80%) rise time of a differential TDR. The impedance profile of a mated connector should fall within the limits shown in Figure 4-2. The impedance profile of the mated connector is defined from the receptacle footprints through the plug cable termination area.

Figure 4-2 Impedance Target for Mated Connector

## 4.2.3 Mated Cable Assemblies

Only the differential impedance and intra-pair skew mated are specified for USB D+/D- signals as shown in Table 4-10.

| Items                     | Descriptions and Procedures                                                                                                                     | Requirements                                                 |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Differential<br>Impedance | EIA 364-108<br>This test ensures that the D+/D- lines of the cable<br>assembly have the proper impedance.<br>For the entire cable assembly.     | 75 ohms min and 105 ohms max.<br>400 ps rise time (20%-80%). |

|                           |                                                                                                                                                 |                                                              |

| Intra-pair Skew           | EIA 364 – 103<br>This test ensures that the signal on both the D+ and<br>D– lines of cable assembly arrive at the receiver at<br>the same time. | 15 ps max.<br>400 ps rise time (20%-80%).                    |

Table 4-10 USB D+/D- Signal Integrity Requirements

| USB 3.1 FRONT-PANEL INTERNAL | <b>CONNECTOR AND</b> | CABLE, REVISION 1.1 |

|------------------------------|----------------------|---------------------|

|------------------------------|----------------------|---------------------|

For SuperSpeed pairs, the design targets defined in Table 4-11 should be met.

| Items                                               | Design Targets                            |  |

|-----------------------------------------------------|-------------------------------------------|--|

|                                                     |                                           |  |

| Differential Insertion Loss for<br>SuperSpeed Pairs | $\geq -0.8 \text{ dB} @ 0.1 \text{ GHz},$ |  |

|                                                     | $\geq$ -2.5 dB @ 2.5 GHz,                 |  |

|                                                     | $\geq$ -3.3 dB at 5.0 GHz,                |  |

|                                                     | ≥ -7.0 dB at 10.0 GHz,                    |  |

| Differential Return Loss for<br>SuperSpeed Pairs    | ≤ −15 dB @ 0.1~5 GHz                      |  |

|                                                     | $\leq -10$ dB @ 5~10 GHz                  |  |

|                                                     | $\leq$ -6.0 dB @ 10~15 GHz                |  |

| Differential NEXT / FEXT                            | ≤ −37 dB @ 0.1~5 GHz                      |  |

| between SuperSpeed Pairs                            | $\leq$ -33 dB @ 5~10 GHz                  |  |

|                                                     | $\leq$ -30 dB @ 10~15 GHz                 |  |

|                                                     |                                           |  |

| Differential NEXT and FEXT                          | ≤ −36 dB @ 0.1~5 GHz                      |  |

| between D+/D- and<br>SuperSpeed Pairs               | ≤ −30 dB @ 5~7.5 GHz                      |  |

Table 4-11 Design Targets for USB 3.1 Internal Cable Assemblies

If those design targets are not met, the integrated parameters shall meet the requirements defined in Table 4-12.

Table 4-12

USB 3.1

Internal Cable Assembly Signal Integrity Requirements

| Items                                                                       | Descriptions and Procedures                                                                                                                              | Requirements                                                                                            |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Differential<br>Insertion Loss Fit at<br>Nyquist Frequencies<br>(ILfitatNq) | ILfitatNq is evaluated at both the SuperSpeed Gen 1<br>and Gen 2 Nyquist frequencies.                                                                    | <ul> <li>≥ -2.5 dB @ 2.5 GHz,</li> <li>≥ -3.3 dB at 5.0 GHz,</li> <li>≥ -7.0 dB at 10.0 GHz,</li> </ul> |

| Integrated<br>Differential Multi-<br>reflection (IMR)                       | $dB\left(\sqrt{\frac{\int_{0}^{f_{max}} ILD(f) ^{2} Vin(f) ^{2}df}{\int_{0}^{f_{max}} Vin(f) ^{2}df}}\right)$                                            | ≤ - 36dB                                                                                                |

| Integrated Return<br>Loss (IRL)                                             | $dB\left(\sqrt{\frac{\int_{0}^{f_{\max}}  Vin(f) ^{2}  SDD21(f) ^{2} ( SDD11(f) ^{2} +  SDD22(f) ^{2}) df}{\int_{0}^{f_{\max}}  Vin(f) ^{2} df}}\right)$ | ≤ -18dB                                                                                                 |

| Integrated<br>Differential Near<br>End Crosstalk on<br>SuperSpeed (INEXT)   | $dB\left(\sqrt{\frac{\int_{0}^{f_{\max}}( Vin(f) ^{2} NEXTs(f) ^{2}+ Vdd(f) ^{2} NEXTd(f) ^{2})df}{\int_{0}^{f_{\max}} Vin(f) ^{2}df}}\right)$<br>where: | ≤ -38 dB, for all SuperSpeed<br>pairs: Tx1-Rx1, Tx1-Rx2, Tx1-<br>Tx2, Tx2-Rx1, and Tx2-Rx2.             |

|                                                                             | NEXTs = NEXT between SuperSpeed pairs                                                                                                                    |                                                                                                         |

|                                                                             | <i>NEXTd</i> = NEXT between D+/D- and SuperSpeed pairs                                                                                                   |                                                                                                         |

|                                                                             | <i>Vdd(f)</i> = Input pulse spectrum on D+/D- pair,<br>evaluated using equation shown in <b>Figure 4-3</b> with Tb<br>(UI) = 2.08 ns.                    |                                                                                                         |

| Items                                                                    | Descriptions and Procedures                                                                                                                                                                                                                                                                                                                                                            | Requirements                                                                                |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Integrated<br>Differential Far End<br>Crosstalk on<br>SuperSpeed (IFEXT) | $dB\left(\sqrt{\frac{\int_{0}^{f_{max}}( Vin(f) ^{2} FEXTs(f) ^{2} +  Vdd(f) ^{2} FEXTd(f) ^{2})df}{\int_{0}^{f_{max}} Vin(f) ^{2}df}}\right)$<br>where:<br>FEXTs = FEXT between SuperSpeed pairs<br>FEXTd = FEXT between D+/D- and SuperSpeed pairs<br>Vdd(f) = Input pulse spectrum on D+/D- pair,<br>evaluated using equation shown in <b>Figure 4-3</b> with Tb<br>(UI) = 2.08 ns. | ≤ -38 dB, for all SuperSpeed<br>pairs: Tx1-Rx1, Tx1-Rx2, Tx1-<br>Tx2, Tx2-Rx1, and Tx2-Rx2. |

| Integrated<br>Differential<br>Crosstalk on D+/D-<br>(IDDXT)              | $dB\left(\sqrt{\frac{\int_{0}^{f_{max}}( Vin(f) ^{2} NEXT(f) ^{2} +  Vin(f) ^{2} FEXT(f) ^{2})df}{\int_{0}^{f_{max}} Vin(f) ^{2}df}}\right)$<br>where:<br>NEXT = Near-end crosstalk from SuperSpeed to D+/D-<br>FEXT = Far-end crosstalk from SuperSpeed to D+/D-<br>fmax = 1.2 GHz                                                                                                    | ≤ -28.5 dB                                                                                  |

| Differential to<br>Common Mode<br>Conversion (SCD12<br>and SCD21)        | The differential to common mode conversion is<br>specified to control the injection of common mode<br>noise from the cable assembly into the host or device.<br>Frequency range: 100 MHz ~ 6.0 GHz                                                                                                                                                                                     | ≤ -20 dB                                                                                    |

Notes:

- 1. A tool to calculate the integrated parameters from the measures S-parameters is provided and it can be downloaded from the USB-IF site: <u>http://compliance.usb.org/files</u>. Select the latest revision of the "FP\_tool" zip file to download.

- fmax = 10 GHz (unless otherwise specified); Vin(f) is defined in Figure 4-3 with Tb (UI) = 100 ps; and Vdd(f) is also defined in Figure 4-3 with Tb (UI) = 2.08 ns.

$$V_{in}(f) = \left| \frac{\sin(\pi f T_r)}{\pi f T_r} \cdot \frac{\sin(\pi f T_b)}{\pi f T_b} \right|$$

$T_b$ =Unit interval=100 ps  $T_r$ =0 to 100% rise time = 0.4 $T_b$

#### Figure 4-3 Input Pulse Spectrum

## 4.3 DC Requirements

#### 4.3.1 Mated connector current carrying requirements

The header/plug connector current carrying capability is defined below, using the 30 degree-C temperature-rise criterion:

- 20-Pin header/plug: 3-A minimum (to support one USB Type-C port).

- 40-Pin header/plug: 2x3.0= 6 A minimum (to support 2 USB Type-C ports).

## 4.3.2 Cable assembly IR drop requirement

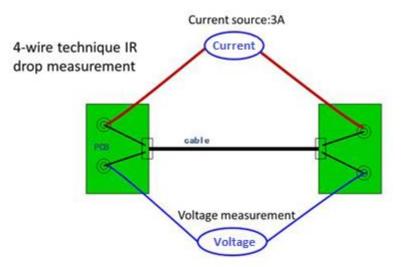

The IR drop of the cable assembly was measured using 4-wire technique, as shown in Figure 4-4.

Figure 4-4 4-wire IR drop testing

The requirement of the IR drop of the cable assembly is in Table 4-13.

|  | Table 4-13 | IR drop | Requirements |

|--|------------|---------|--------------|

|--|------------|---------|--------------|

| Items       | Descriptions and Procedures                                                                                          | Requirements |

|-------------|----------------------------------------------------------------------------------------------------------------------|--------------|

| Ground pins | <ul> <li>4-wire technique is used, 3A current</li> <li>All ground pins are connected together for testing</li> </ul> | 185 mV max   |

| VBUS pins   | <ul> <li>4-wire technique is used, 3A current</li> <li>All VBUS pins are connected together for testing</li> </ul>   | 200 mV max   |